**MULTISCALE TRANSIENT THERMAL ANALYSIS OF MICROELECTRONICS**

# Electronics COOLING

SEPTEMBER 2015 electronics-cooling.com

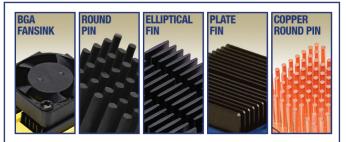

# HEATSINK GEOMETRY TOPOLOGY

### **An Additive Design Methodology for Identification**

INSIDE

**NEW! THERMAL LIVE** ADVANCE PROGRAM

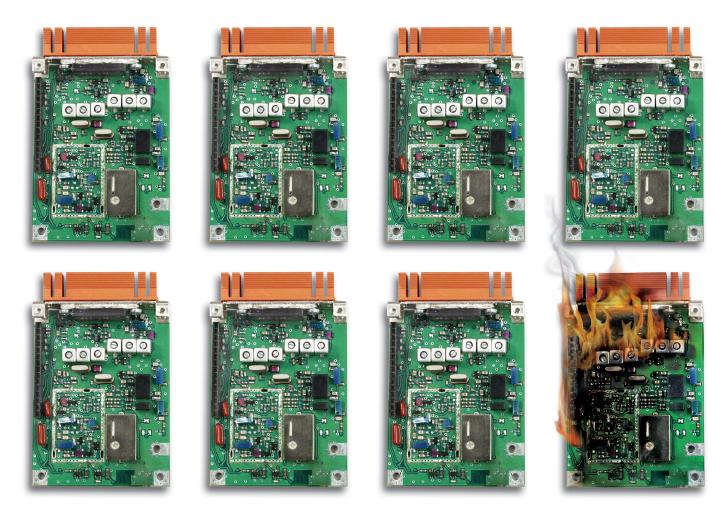

## 7 out of 8 electronic devices recommend **Bergquist Thermal Clad® Substrates**

(The 8th device was unavailable for comment)

### World leading OEMs choose Bergquist.

For 25+ years Thermal Clad® has been effectively used in industries such as high-power LED lighting, automotive, power conversion, motor control, aerospace/military, computer, telecommunications and more.

### Don't get burned - Choose your insulated metal substrates carefully.

Bergquist supplies the world with some of the best solutions in the business:

- Long-term dielectric strength

- Low thermal impedance

- U.L. Listed, high maximum operating temperature

- Long-term temperature testing

#### www.bergquistcompany.com 1.800.347.4572

952.835.2322 fax 952.835.0430 18930 West 78th Street • Chanhassen, Minnesota 55317

### **Explore your dielectric** options with a **FREE Sample Kit.**

This kit contains samples of select Bergquist Thermal Substrates to allow you to select the best option that fits your application. To receive your kit, call 1-800-347-4572 or qualify online at www.bergquistcompany.com/coolkit

BERGQUIST

Vith More Thermal Clad®MCPCB

Options, You Can En

### CONTENTS

2 **EDITORIAL** Peter Rogers, Editor-in-Chief, September 2015

### **THERMAL FACTS**

Numerical Modeling without Supporting Experimentation Peter Rogers, Editor-in-Chief, September 2015

12 **TECHNICAL BRIEF**

Effective Heat Spreading Angle Dirk Schweitzer, Infineon Technologies AG

### 16

### **CALCULATION CORNER**

On-site Cogeneration for Reducing Data Center Primary Energy Use Dustin W. Demetriou. IBM

### 22 **COOLING MATTERS**

News of Thermal Management Technologies

39 **INDEX OF ADVERTISERS**

### FEATURE ARTICLES

Advance Program

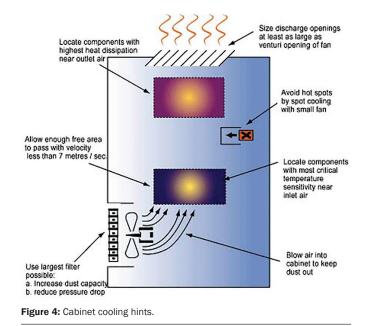

28 **MOST POPULAR ARTICLE ARCHIVE:** ALL YOU NEED TO KNOW ABOUT FANS

Mike Turner Comair Rotron

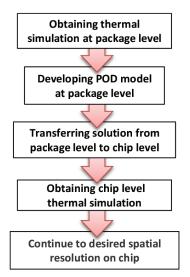

32 **AN EFFICIENT APPROACH FOR MULTI-SCALE THERMAL MODELING OF INTEGRATED CIRCUITS**

Banafsheh Barabadi3, Satish Kumar<sup>1</sup>, Valeriy Sukharev<sup>2</sup>, Yogendra K. Joshi<sup>1</sup>

<sup>1</sup>G.W. Woodruff School of Mechanical Engineering at Georgia Institute of Technology; <sup>2</sup>Mentor Graphics Corporation; <sup>3</sup>Massachusetts Institute of Technology

# THERMAL LIVE

A BRAND NEW EVENT FEATURING PRACTICAL THERMAL MANAGEMENT **TECHNIQUES & TOPICS**

FREE TO ATTEND FROM THE COMFORT OF YOUR OWN CHAIR

**OCTOBER 6-8, 2015** thermallive2015.com

AN ADDITIVE DESIGN METHODOLOGY FOR HEATSINK GEOMETRY TOPOLOGY IDENTIFICATION

Robin Bornoff, John Parry, Mentor Graphics Corporation

# **Editorial**

### Are Graduate Engineers being Effectively **Educated for Today's Workplace?**

Peter Rodgers, Editor-in-Chief, September 2015

**ONTINUING** the June Editorial [1] theme, which discussed the societal aspects of enticing today's youth into pursuing a career in the engineering profession, this editorial explores if the capabilities of today's young engineering graduate are being effectively harnessed upon graduation. Otherwise said, is the educational experiences of today's engineering graduates in sync with

As a university professor, my greatest time sink is neither teaching nor research, but undertaking departmental duties for its baccalaureate program accreditation. Using a Shakespearean quote, to convey how I

may feel at times about this task, "Though this be madness, yet there is method in't." The time and efforts invested towards accreditation should be ultimately rewarded when a young graduate finds the opportunity to apply his/her acquired knowledge, skills and competences upon employment. To achieve this, a structured and ever-evolving engineering education is required. The effectiveness of engineering education is typically continuously assessed and improved through external accreditation by bodies such as ABET [2], a widely recognized U.S. and international accreditor of engineering university programs. For an ABET-accredited engineering program, eight general criteria (Criterion 1 to 8) that encompass assessment of the student, faculty, program, and institution are required to be met. Criterion 3, student learning outcomes (SLOs), assesses what students are expected to know and be able to do by the time of graduation. The level of achievement of eleven sub-criteria, SLOs 3(a) to 3(k), is monitored to achieve Criterion 3. Accreditation provides confidence to students, employers, and society that the engineering program meets a high quality standard to produce graduates prepared to enter a global workforce.

One of the most effective venues to assess SLOs 3(a) to 3(k) is through a Senior-level "Capstone Design" course. In this course, engineering students work in teams to design, build, and test prototypes having real world applications, incorporating engineering standards and multiple realistic constraints. Typically at the end of this course, students showcase their efforts at a "Senior Design Expo," which in many instances doubles as a job fair.

In the context of the above educational approach, are our young graduates getting the opportunity to fully apply the knowledge, skills, and competences acquired through education in today's engineering workplace? Rather than approaching this concern as a rhetorical question, let's explore a concerning answer.

Firstly, rather than the majority of graduates being feted, a recent U.S. employer survey [3] judge them to be ill-prepared for today's workplace. Only 25% of employers felt that recent graduates are well prepared in critical thinking and analytic reasoning, written and oral communication, complex problem solving, innovation and creativity, and applying knowledge and skills to real world settings. On the other hand, students were found to feel far more prepared (i.e., above 60%) in these key areas. Based on the same survey, employers strongly endorsed broad and project-based learning as the best preparation for career opportunity and long-term success. How can the above disconnect between the employer's and graduate's perception of his/her capabilities be addressed? Is the Capstone Design experience, which develops and assesses the level of achievement of most key educational criteria, inadequately conceived or utilized?

For the electronics thermal management community, employers should realize that opportunities exist to contribute to undergraduate education through involvement in Capstone Design activities. In the long term, this could assist to better sync young graduates' and employers' expectations.

Electronics Cooling recognizes that continued education is extremely important. This year, we announce a unique opportunity to learn for all engineers in the thermal management field -Thermal Live. This is a brand new, free online event that will take place Oct. 6-8, 2015, and will offer webinars and roundtables on thermal management topics. Please join us for this special event. Visit www.thermallive2015.com for more information.

#### References

[1] Guenin, B., 2015, "Editorial: The Joy of Engineering," *ElectronicsCooling*, June, pp. 1. [2] ABET, http://www.abet.org/, last retrieved August 26, 2015.

www.electronics-cooling.com

#### ASSOCIATE TECHNICAL EDITORS

Bruce Guenin, Ph.D. Principal Hardware Engineer, Oracle bruce.guenin@oracle.com

Peter Rodgers, Ph.D. Professor, The Petroleum Institute prodgers@pi.ac.ae

Jim Wilson, Ph.D., P.E. Engineering Fellow, Raytheon Company isw@ravtheon.com

#### PUBLISHED BY

ITEM Media 1000 Germantown Pike, F-2 Plymouth Meeting, PA 19462 USA Phone: +1 484-688-0300; Fax:+1 484-688-0303 info@electronics-cooling.com; electronics-cooling.com

CONTENT MANAGER

Belinda Stasiukiewicz bstas@item-media.net

**MARKETING DIRECTOR** Dawn Hoffman

dhoffman@item-media.net

**MARKETING SPECIALIST**

Erica Osting eosting@item-media.net

**EDITORIAL ASSISTANT**

Allison Titus atitus@item-media.net

PRESIDENT Graham Kilshaw

gkilshaw@item-media.net

#### REPRINTS

Reprints are available on a custom basis at reasonable prices in quantities of 500 or more Please call +1 484-688-0300.

#### SUBSCRIPTIONS

Subscriptions are free. Subscribe online at www.electronics-cooling.com. For subscription changes email info@electronics-cooling.com.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, or stored in a retrieval system of any nature, without the prior written permission of the publishers (except in accordance with the Copyright Designs and Patents Act 1988).

The opinions expressed in the articles, letters and other contributions included in this publication are those of the authors and the publication of such articles, letters or other contributions does not necessarily imply that such opinions are those of the publisher. In addition, the publishers cannot accept any responsibility for any legal or other consequences which may arise directly or indirectly as a result of the use or adaptation of any of the material or information in this publication.

Electronics Cooling is a trademark of Mentor Graphics Corporation and its use is licensed to ITEM. ITEM is solely responsible for all content published, linked to, or otherwise presented in conjunction with the Electronics Cooling trademark.

# One-Stop Shore Stop

Industries that we support: Cloud Computing Medical Equipment (MRI) Wind Power Solar Power Semiconductor Test Equipment Consumer Electronics Telecom

### Malico Inc.

US Local Contacts Chino CA Tel CA Mobile San Jose MA Mobile **Boston** Dallas TX Tampa FL Mobile Website:www.malico.com

Tel :909-993-5140 E-mail : davidliang@malico.com Mobile :408-605-1616 E-mail : ky@maxpros.com Mobile :978-771-9285 E-mail : jhmclean@malico.com Mobile :214-514-9836 E-mail : annylo@malico.com Mobile :401-480-4752 E-mail : charlierandall@malico.com

www.malico.com

roperties of their respective holder

# THERMAL LIVE

### October 6-8, 2015 - www.thermallive2015.com

Thermal Live™ is a brand new concept in education and networking in thermal management - a FREE 3-day online event for electronics and mechanical engineers to learn the latest in thermal management techniques and topics. Produced by Electronics Cooling® magazine, and launching in October 2015 for the first time, Thermal Live™ features live webinars, roundtables, whitepapers, and videos ... and there is no cost to attend!

### **TECHNICAL PROGRAM**

### DAY 1 - TUESDAY . OCTOBER 6

### **KEYNOTE SPEAKER**

Oct. 7, 11:00 a.m. – 11:45 a.m. (EDT)

### *A Practical Guide to Using Two-Phase Heat Sinks* Oct. 6, 12:15 p.m. – 1:00 p.m. (EDT)

### OVERVIEW

Overview: Two-phase devices are incredible heat conductors and significantly boost heat sink performance. We'll present a practical guide to using both heat pipes and vapor chambers: similarities, differences, operating parameters, mounting options, common mistakes, best uses, examples, and performance modeling.

### **SPEAKER**

George Meyer is a thermal industry veteran with over three decades experience in electronics thermal

management. He currently serves as CEO/CTO of Celsia Technologies. Mr. Meyer has been instrumental in establishing Asian operations, developing new technologies, key customer relationships, managing the product portfolio, and growing sales into the computer, telecommunications, networking, LED lighting, medical, laser and military markets. He holds over 70 patents in heat sinks and heat pipe technologies.

### **DAY 1 CONTINUED**

### **ROUNDTABLE**

### Liquid Dispensed Thermal Interface Materials (TIMs)

Oct. 6, 1:30 p.m. – 2:15 p.m. (EDT)

### **OVERVIEW**

This roundtable will discuss how effective thermal management is key to ensuring consistent long-term performance and reliability in electronic devices. With an increasing variety of electronic applications demanding smaller packaging, higher power, and lower cost, the need for innovative high performance, low cost thermal solutions continues to grow.

While there are many pad-form solutions available on the market, ever-increasing customer costs inherent with designing, documenting, shipping, storing, managing and assembling a multitude of die-cut parts in varying sizes continues to challenge design engineers. Join a panel of thermal management experts during this roundtable, where they will discuss how high performance liquids with unique characteristics are designed to improve overall thermal performance and reliability for thermal engineers.

#### Moderator: Mark Amberg Market Manager -

Mark Amberg has been with The Bergquist Company, now a division of Henkel AE, for 18 years. He has held the roles of Automotive Market Manager and Automotive Business Development Manager for the last ten years.

Liquid Dispensed TIMs Roundtable information continued on next page

### **DAY 1 CONTINUED**

Liquid Dispensed TIMs Roundtable information continued from previous page

#### Panelists:

Lonnie Helgeson Product Line Manager Lonnie Helgeson is the Product Line Manager overseeing the Gap Filler product line for Henkel. His responsibilities

include the identification and prioritization of strategic business opportunities to enhance the Liquid Thermal Interface Materials (TIMs) portfolio. With over thirty years of experience in the high tech

market, he offers great insight in this fast paced globally competitive marketplace.

Ryan Verhulst Scientist Engineer -

Ryan Verhulst is a Research & Development engineer working on thermal interface materials. He has been with Henkel (formerly Bergquist) for 8 years. His education is in material science and he has experience working with ceramic powders, adhesives and sealants, and a wide variety of polymer chemistries.

**Rvan Verhulst**

John Timmerman Senior Scientist Engineer -

John is a senior research engineer with Henkel, whose main focus is high performance thermal interface materials, thermally conductive adhesives, and EMI absorbing materials. He has been with Henkel for 8 years and graduated from the University of Washington in 2003 with a Ph.D. in chemical engineering, where he researched thermal cycling of com-

posite materials. Tom Harris Field Applications Engineer-

Tom Harris uses his Process Engineering, Automation and Customer Service Experience to assist Henkel AEH customers implement and troubleshoot Automated Liquid TIM Dispensing in their manufacturing processes. He also directs Henkel's Dispense Alliance Program, and Automated Dispensing Technical Knowledge-base. He holds a Six Sigma Green Belt as well as an M.B.A. and B.S. in Engineering.

Tom Harris

### **WEBINAR**

Thermal Management Challenges, Requirements and Solutions for the Electronics Industry

Oct. 6, 2:45 p.m. - 3:30 p.m. (EDT)

#### **OVERVIEW**

This webinar will discuss the key thermal properties involved in TIM decisionmaking, the challenging thermal requirements of key applications, a comparison of solutions available to the marketplace, and the promise of next-generation PCMs designed to meet the constantly changing demands of the electronics industry.

#### **SPEAKER**

Glenn M. Mitchell, Ph.D is the Director of Technology for Honeywell Electronic Materials. He has a Ph.D. in Analytical Chemistry from Drexel University,. His focus is new molecule and process development and optimization for the electronics, semiconductor, and solar industries. His areas of expertise is ultra-trace impurity analysis and analytical method development, advanced statistical analysis and chemometrics, etch, deposition, and more.

#### **SPEAKER**

Chris Caylor is the Technical Director of the Electronics Cooling Business Unit at Phononic. He earned his Ph.D.

### DAY 2 - WEDNESDAY . OCTOBER 7

### **WEBINAR**

### Small Form Factor Cooling with Jet Air Mover Technology

Oct. 7, 12:15 p.m. - 1:00 p.m. (EDT)

### **OVERVIEW**

Jet Cooling Technology has far reaching implications on small form factor design. These novel air movers increase the design space, flexibility and performance of a wide range of products, from consumer handhelds to LEDs to outdoor telecom.

Lee Jones joined Aavid-Thermalloy in the summer of 2014. As part of the team at Nuventix, Lee led technical and product development efforts to create the world's most compact and reliable turbulent air coolers. His role was an inside-outside one spanning SynJet engineering and customer product and advanced development teams to tailor SynJet solutions that would enable breakthrough products for customers. At Aavid he performs a similar role leading the product management efforts of SynJet development globally. Lee has a Bachelor's Degree in

Mechanical Engineering from Rochester Institute of Technology, and a Master's Degree in Mechanical Engineering from The University of Texas at Austin.

### ROUNDTABLE

### Extending Moore's Law through Innovative Active Cooling

Oct. 7, 1:30 p.m. - 2:15 p.m. (EDT)

#### **OVERVIEW**

This roundtable will be a discussion with thermal engineers, hardware designers, and architects on the merits of passive fan assists, water cooling, and variable assist active cooling as it pertains to high density electronics. Specifically, the discussion will focus on the pros and cons of different approaches to electronics cooling and the impact on system performance from component temperature control, form factors, power consumption and cost trade-offs. Attendees will gain an understanding of the most recent advances in electronics cooling, including the ability to use active heat pumps based on thermoelectric devices, to provide superior cooling performance while minimizing the aggregate capex and opex costs.

> in Chemistry from the University of California at Berkeley. He is an engineering, research and product leader with over 10+ years in managing engineering programs and teams. Chris also has 6+ years experience in winning and managing government programs from diverse sources such as DoD, DoE and DARPA.

### **DAY 2 CONTINUED**

### **WEBINAR**

### *Liquid Cooling – Practical Guidelines to Design & Manufacture*

Oct. 7, 2:45 p.m. – 3:30 p.m. (EDT)

#### **OVERVIEW**

Industry trends continue to produce smaller footprints with higher power densities. In some cases, Liquid Cooling is the answer for cooling your application. This discussion will go over the basic design and structure of several standard and custom liquid cooling solutions while highlighting the manufacturing process most appropriate for your application.

#### **SPEAKER**

Mark Pelillo is the Director of Engineering at Wakefield-Vette. Mark has been

in the electronics cooling design industry for over 25 years and has been a pivotal part in introducing new technologies to the marketplace. Mark earned his engineering degree at Clarkson University. Mark has been with Wakefield-Vette since 2005, where he leads the engineering team. This team supports existing customer challenges, while researching and introducing new technologies to market. Mark's vast experience not only with design but in manufacturing, allows Wakefield-Vette's customers to improve their thermal performance while simplifying the manufacturing steps to meet specifications.

### **WEBINAR**

DOW CORNING

### IMAGINE: Drawing Out Heat, Leaving in Performance and Reliability

Oct. 7, 4:00 p.m. – 4:45 p.m. (EDT)

#### **OVERVIEW**

In this webinar, attendees will be able to see key milestones in the evolution of thermal interface materials that help ensure today's electronics performance and reliability. They will also be able to learn about proven, effective thermal management solutions for basic devices to complex electronics architectures and get expert insights on best practices and material types to meet specific design objectives. Attendees will discover how advanced thermal management solutions make gamechanging differences in a diverse range of industries and will see brief case studies of electronics applications with thermal management excellence.

### **DAY 3 - THURSDAY . OCTOBER 8**

### WEBINAR GRAFTech International

### High Temperature TIM for Power Modules that Eliminates Pump-out and Dry-out Failures

Oct. 8, 11:00 a.m. - 11:45 a.m. (EDT)

### **OVERVIEW**

In this webinar, attendees will learn about developed compressible graphite foils to provide a high reliability, high temperature (over 200°C) TIM that addresses the thermal demands and out-of-flatness issues of large high power switching modules. This new material will eliminate the compromise between thermal performance, maximum operating temperature, reliability, cost, and ease of installation. Un-

like any other graphite or soft metal TIMs that provide compression of less than 10%, HITHERM™ HT-C3200 compressible graphite pads have a nominal starting thickness of 200 microns and compress down to 50 microns at 100 PSI (~700 kPa) reducing the total thermal resistance between the two surfaces while eliminating pump-out and dry out failures common with greases and phase change materials.

### SPEAKER

Prashanth Subramanian - As the manager of the New Product Development group at Graftech International, a

world leader in graphite material science, Prashanth is responsible for the development and commercialization of solutions to the consumerelectronics and Thermal Interface for high powered device markets. Prior to joining Graftech, Prashanth worked at SUMCO USA in the Development Engineering group providing solutions to the high-voltage device market. Prashanth holds a degree in Electronics Engineering from Shivaji University (India) and a M.B.A. from The Ohio State University.

### WEBINAR

### PCB Design Strategies in Handheld Devices

Oct. 8, 12:15 p.m. - 1:00 p.m. (EDT)

### **OVERVIEW**

This presentation reviews factors influencing thermal design in consumer handheld devices from touch temperature const raints, dissipating heat effectively from high power density components, tight tolerance geometry, through to varying power modes from user operation. Thermal management studies ideally allow accurate, rapid, physical modeling to make decisions on materials, components and layout beside power control feedback to achieve performance & target lifetime with reduced testing requirements. Simulation methods are discussed and closer integration with both electronic and industrial design functions as part of overall product development.

PCB Design Strategies Webinar information continued on next page

www.thermallive2015.com

### **DAY 3 CONTINUED**

PCB Design Strategies Webinar information continued from previous page

### SPEAKER

John Wilson joined Mentor Graphics Corporation, Mechanical Analysis Division (formerly Flomerics Ltd) after receiving his BS and MS in Mechanical Engineering from the University of Colorado at Denver. Since joining in 1999, John has worked on or managed more than 70 thermal and airflow design projects. His modeling and design knowledge range from component level to Data Centers, heat sink optimization and compact model development. John has extensive experience in IC package level test and analysis correlation through his work at Mentor

Graphics' Fremont based Thermal Test Facility. Currently John serves as an Electronics Product Specialist..

Mentor Graphics is a company that enables companies to develop better electronic products faster and more cost-effectively. Their innovative products and solutions help engineers conquer design challenges in the increasingly complex worlds of board and chip design.

### www.thermallive2015.com

### **DAY 3 CONTINUED**

### WEBINAR

### MATERION

Composite Metal Heat Spreaders in Handheld Electronics Design

Oct. 8, 1:30 p.m. – 2:15 p.m. (EDT)

### **OVERVIEW**

This webinar will discuss how omposite metal solutions provide design opportunities for improved heat spreading and mechanical rigidity in space-constrained consumer devices. Utilizing composites in the design of structural components allows existing device features, such as frames and EMI shields, to dissipate thermal loads from high power heat sources without the need for secondary heat spreaders. Design

### considerations and materials performance properties are discussed with an eye toward cooler, stiffer devices.

#### SPEAKER

Aaron Vodnick joined Materion in 2012. He eads global market and product development initiatives for composite metal systems, specifically unconventional thermal and structural materials for consumer devices. Aaron has a Bachelor's Degree in Materials Engineering from the University of Minnesota Twin Cities, and a Ph.D. in Materials Engineering from Cornell University.

### Numerical Modeling without Supporting Experimentation

### Peter Rodgers Editor

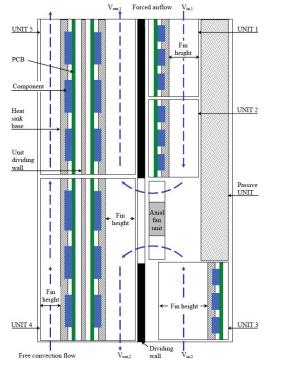

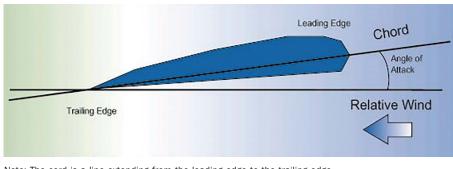

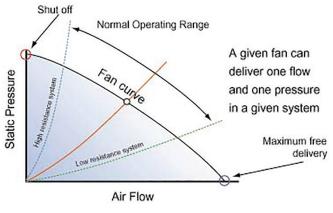

AN MODELLING is one of the most critical aspects of the analysis of forced-air-cooled systems. Lasance [1] summarized the challenges of modeling air movers such as fans and key factors that need to be taken into consideration. Such factors include the need to model the fan hub, and to account for the swirl velocity coefficient.

In addition to the above challenges, Grimes et al. [2] found that vendor fan performance characteristic curves published in manufacturer catalogs can typically be only approximately reproduced by clients under standard conditions, although vendor data is supposed to be generated in accordance with BS Standard 848. This standard specifies an acceptable uncertainty of  $\pm 2$  % for all measurements of fan flow.

Furthermore, the potential adverse influence of the operating environment on fan curve performance is often overlooked in numerical work, and is the focus of this article. Constricted installation spaces in electronic systems can result in significant fan performance losses [3-5], as illustrated in for example [3]. To demonstrate the potential significance of this oversight, the results of a computational fluid dynamics (CFD) benchmark undertaken for a mock-

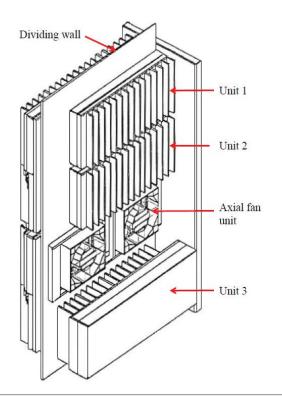

Figure 1: System geometry and internal airflow patterns.

### High-performance heatsinks at your fingertips.

CTS high-performance, low-profile heatsinks cool your integrated circuits with superior thermal resistance compared to others in the industry and with lowest cost per dissipated Watt. Our LED lighting solutions use advanced technologies including high-density fins and special thermal coatings. CFD analysis tools help our engineers find the best solutions for your thermal challenges. Our thermal solutions are at your fingertips.

FPGA Heatsink Design Guide Catalog for Xilinx's ICs at: www.ctscorp.com/components/heat\_sinks.asp

For more information visit www.ctscorp.com or send an email to frequencysales@ctscorp.com in 8+ C []

| System cooling configuration | Fan location and operational mode                                                                                                                | Airflow configuration                                                                                                                                                                                                                                                                                                                                      |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A                            | • Axial fan unit<br>mounted within<br>the enclosure, but<br>unpowered                                                                            | All heat sinks are passively cooled, with air entering the enclosure through<br>Units 3 and 4 heat sinks, and vertically exhausting through Units 1 and 5<br>heat sinks.                                                                                                                                                                                   |

| В                            | <ul> <li>Axial fan unit<br/>mounted 50 mm<br/>beneath the<br/>enclosure (Units 3<br/>and 4)</li> <li>Fan operated in<br/>blowing mode</li> </ul> | Forced air enters through Unit 3 heat sink and Unit 4 right-hand side heat<br>sink, and exhausts directly through Unit 1 heat sink and Unit 5 right-hand<br>side heat sink. Unit 4 and Unit 5 left-hand side heat sinks are passively<br>cooled.                                                                                                           |

| C                            | <ul> <li>Axial fan unit<br/>mounted within<br/>the enclosure,<br/>and powered</li> <li>Fan operated in<br/>sucking mode</li> </ul>               | Units 1, 2 and 3 heat sinks, and Units 4 and 5 right-hand side heat sinks, are cooled by forced convection. Units 4 and 5 left-hand side heat sinks are passively cooled. In forced convection cooling, air is drawn into the enclosure through Units 1 (Vin_1) and 3 (Vin_2) heat sinks, and exhausts through Units 4 (Vout_2) and 5 (Vout_1) heat sinks. |

Table 1 : System cooling configurations.

Note: The geometry of cooling configurations A, B and C is shown in Figure 1

up telecommunication system to assess the accuracy of fan curve modeling is presented.

As shown in *Figure 1*, the system is comprised of five mockup heat dissipation units (designated as Units 1 to 5), each having a printed circuit board (PCB) assembly mounted to a heat sink. PCB heat dissipation was experimentally simulated using board-mounted resistors. Units 1, 2, and 3 are comprised of a single PCB-heat sink assembly, whereas Units 4 and 5 both have two PCBs separately mounted to heat sinks.

Three system cooling configurations are considered, that are summarized in Table 1. Note that cooling configuration C could be considered as a poor thermal design in terms of fan location, but serves here to illustrate modeling challenges.

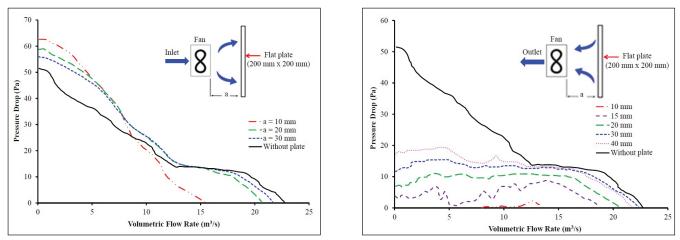

For cooling configuration C, the influence of the restricted environment on fan performance requires to be considered. In the absence of a physical prototype, the fan performance curve was obtained from the vendor and was generated in accordance with BS Standard 848. In addition, the influence of a single 200 mm x 200 mm flat plate obstruction mounted at varying distances from the fan, ranging from 10 mm to far field, on either the pressure or suction side, as illustrated in *Figure 2*, is assessed. As expected [3], the suction side is found to be more sensitive to the presence of an obstruction than the pressure side.

The airflows entering and exiting the system enclosure were measured using hot wire anemometry to determine fan flow rate. Operating temperature was measured in steady state conditions at selected locations, and the electrical power dissipated as heat by each unit was also measured. These latter two measurements combined permitted the calculation of the unit thermal resistance.

A complete system level CFD model was constructed using an industry standard software for each of the three enclosure cooling configurations in Table 1, and was validated for individual units using experimental measurements conducted in wind tunnel and still air enclosures. For each of the three enclosure cooling configurations, the model predictive accuracy is assessed in terms of the measured heat sink thermal resistance and fan flow rate.

As shown by the results presented in Table 2, very good agreement was found between numerical predictions and measurements for cooling configurations A and B. However significant discrepancies in heat sink thermal resistance exist for configuration C, which is attributed to inaccurate prediction of the fan airflow rate.

### SUMMARY

This article illustrates that without supporting measurements, predicting complex system thermal performance is a challenge because of the non-availability of accurate fan flow modeling data, applicable to the system geometry and cooling configuration under analysis. The accuracy of the CFD software itself is unlikely to be a significant source of error in this instance.

Note: a = separation distance between fan and flat plate obstruction.

Figure 2: Measured change in axial fan performance characteristic curve caused by the flat plate obstruction.

### REFERENCES

Clemens J. M. Lasance, The Conceivable Accuracy of Experimental and Numerical Thermal Analyses of Electronic Systems, IEEE Transactions on Components and Packaging Technologies, Vol. 25, No. 3, 2002, pp. 366-382.

Grimes, R., Davies, M., Punch, J., Dalton, T., and Cole, R., 2001, "Modeling

Electronic Cooling Axial Fan Flows," Transactions of the ASME, Journal of Electronic Packaging, Vol. 123, pp. 112- 119.

[3] Harmsen, S., "Equipment Fans for Electronic Cooling: Function and Behaviour in Practical Application, verlag modeme industrie, 1991.

[4] Hill, T.B., and Hill, C.H., "Effects of Electronic Enclosure Layout on Fan Performance," ASME Winter Annual Meeting, Paper Number 90-WA-EEP-6, 1990.

[5] Deiters, T., and Hill, T.B., "Correlation of Experimental Measurements to Computer Modeling of a Forced Convection Cooled Electronics Enclosure, ASME Winter Annual Meeting, Paper Number 91-WA-EEP-36, 1991.

| System<br>cooling<br>configuration | Finding                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А                                  | Predicted heat sink thermal resistances are within 10% of measurement.                                                                                                                                                                                                                                                                                                                         |

| В                                  | Predicted fan flow rate and heat sink<br>thermal resistance are both within 10% of<br>measurement                                                                                                                                                                                                                                                                                              |

| С                                  | <ul> <li>55% discrepancy between predicted fan<br/>airflow using nominal vendor fan curve and<br/>measurement exists</li> <li>40% discrepancy between predicted fan<br/>airflow using suction side fan curve and<br/>measurement for a = 30 mm exists</li> <li>Approximately 20% to 30% discrepancy<br/>between predicted heat sink thermal resis-<br/>tance and measurement exists</li> </ul> |

Table 2: Discrepancy in unit thermal resistance between numerical predictions and measurements.

### **Effective Heat Spreading Angle**

Dirk Schweitzer Infineon Technologies

### INTRODUCTION

**O ACCURATELY COMPUTE THE THERMAL RESISTANCE** of a layered structure, such as the Junction-to-Case thermal resistance of a power semiconductor, the heat spreading inside the structure has to be considered. The calculation of the spreading resistance is not a trivial problem [1] and analytical solutions exist only for extremely simple geometries. Using Finite Element Analysis (FEA) the heat spreading and resulting temperature distribution can be accurately computed. But for a quick and simple analysis of the spreading resistance the thermal engineer has to resort to rules of thumb such as the 45° spreading angle [2, 3], or to approximation formulas which can be found in literature [1, 4]. This article presents an alternative approach, namely the concept of the effective heat spreading angle [5].

### **EFFECTIVE HEAT SPREADING PROFILE**

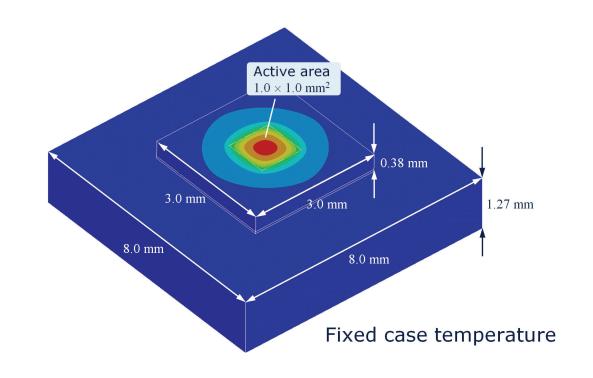

To explain this concept we consider a silicon chip on a copper (Cu) leadframe as shown in figure 1. A power of  $P_H = 10$  W is dissipated homogeneously on an active area of  $1.0 \times 1.0$  mm<sup>2</sup> on the  $3.0 \times 3.0$  mm<sup>2</sup> chip whereas the bottom temperature of the leadframe is kept constant (ideal cooling).

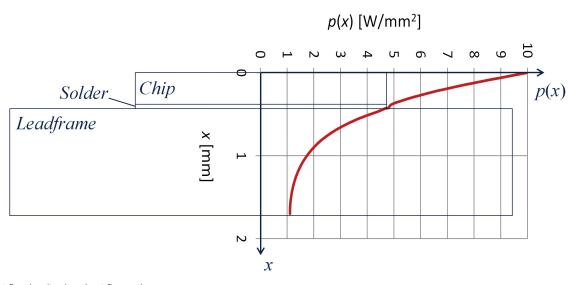

Monitoring the local heat flux density p(x) from the center of the die surface to the center of the bottom surface (x being the distance from the heat source), *Figure* 2, we notice that the heat flux density drops continuously from initially 10 W/mm<sup>2</sup> to about 1 W/mm<sup>2</sup> at the bottom. Obviously the heat spreading is the reason for

**Dirk Schweitzer** works as a simulation engineer at Infineon Technologies AG in the fields of thermal and mechanical analysis. With more than 15 years of experience in electronics cooling he has extensive experience in thermal simulation and measurement of semiconductor devices. As an active member of the JEDEC JC-15 committee on thermal standards he was one of the main contributors to the development of a transient measurement standard for Rth-JC, a work which was acknowledged by the Harvey Rosten Award of Excellence in 2010. Prior to his employment at Infineon he worked as a research assistant at the University of Augsburg, studying crystal growth processes by means of molecular dynamics simulations. He received his degree in Physics at the University of Augsburg, Germany.

the decreasing heat flux density. If the cross sectional area of the heat flow path was constant the heat flux density would also remain constant throughout the structure. Since the variation of the heat flux density is closely related to the amount of heat spreading the obvious idea was to derive a measure for the spreading angle from the derivative dp/dx of the heat flux density.

For simplification we shall assume that the heat flux is homogenously distributed over each cross section A(x) of the heat flow path (which is not the case in reality). At each position x the product of cross-sectional area A(x) and heat flux density p(x) equals the total power dissipation  $P_{H}$ .

$$A(x)p(x) \tag{1}$$

Furthermore we shall assume that the shape of the heat flow cross section does not change as the heat propagates (which is not true either); i.e.: in this case it remains a square area independent of the distance x from the chip surface. For the half side length y(x) of this square we obtain:

Figure 1: Silicon chip on Cu leadframe (solder die attach).

Figure 2: Heat flux density along heat flow path.

$$y(x) = \frac{1}{2}\sqrt{A(x)} = \frac{1}{2}\sqrt{\frac{P_{H}}{p(x)}}$$

(2)

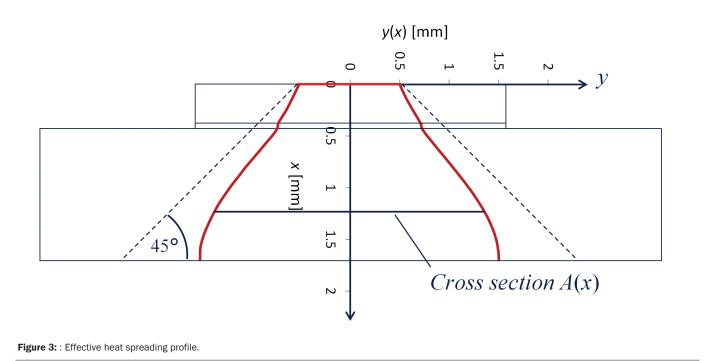

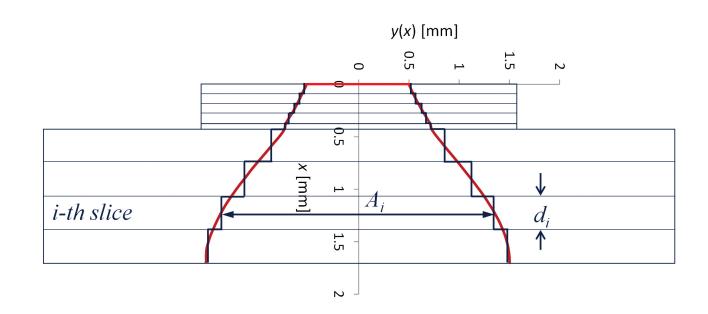

Plotting y(x) vs. distance x we obtain the *effective heat spreading profile (figure 3)*. We call this the *effective* heat spreading profile as opposed to the real spreading profile because it has been derived for above non-true assumptions. This approach is justified by the fact that we can use the effective heat spreading profile to calculate the spreading resistance within any desired accuracy. *Figure 4* shows a discretization

of the effective spreading cone. In this example chip and leadframe are each subdivided into 4 slices and the die attach is represented by one more slice. The temperature drop  $\Delta T_i$  across each slice can be calculated from the density pi of the heat flux passing through it, its thickness  $d_i$ , and its thermal conductivity  $\lambda_i$ :

$$\Delta T_i = \frac{p_i}{\lambda_i} d_i \tag{3}$$

Because the cross sectional area  $A_i$  of each slice has been

constructed such that  $A_i = P_H/p_i$  we have:

$$\Delta T_i = \frac{P_H}{A_i \lambda_i} d_i = P_H \theta_i \quad \text{with} \quad \theta_i = \frac{d_i}{A_i \lambda_i}$$

(4)

where  $\theta_i$  represents the thermal resistance of the *i*-th slice such that if we multiply it by the total heat flux  $P_H$  we obtain the correct temperature difference across that slice. Therefore the sum over all slices:

$$\theta = \sum_{i=1}^{n} \theta_i = \sum_{i=1}^{n} \frac{d_i}{A_i \lambda_i}$$

(5)

approximates (and for  $n \rightarrow \infty$  exactly returns) the thermal resistance of the structure. In practice even a rather coarse discretization of the effective heat spreading profile as in figure 4 results in a quite good approximation of the actual thermal resistance (<1% error in this case). Application of the popular 45° heat spreading assumption on the other hand would overestimate the size of the spreading cone and thus result in a too low value for the thermal resistance (*figure 3*).

### **EFFECTIVE HEAT SPREADING ANGLE**

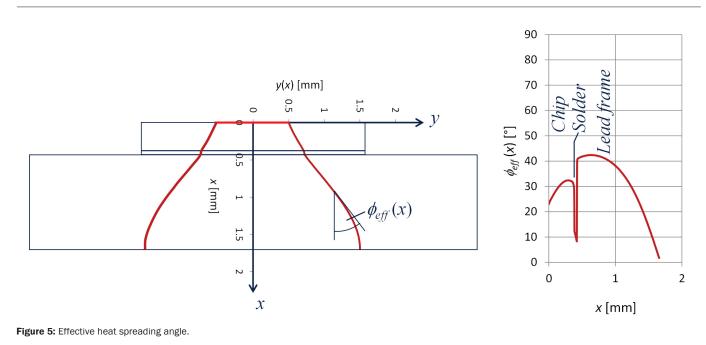

Based on the effective heat spreading profile y(x) the corresponding effective spreading angle can be easily computed *(figure 5)*:

$$\tan\phi_{eff} = \frac{dy}{dx} \tag{6}$$

Using Equation (2) we obtain for the heat spreading cone with square cross section:

$$\tan\phi_{eff} = -\frac{1}{4}\sqrt{\frac{P_H}{p(x)}}\frac{1}{p(x)}\frac{dp}{dx}$$

(7)

### **BENEFITS OF THE EFFECTIVE HEAT SPREADING CONCEPT**

The attentive reader will now object: That is all well and good but how do I know the heat flux density p(x) along the heat flow path which is required to calculate the effective spreading profile? Which is a valid objection since p(x) can only be obtained by Finite Element (FE) simulation. There would be little motivation to perform a FE simulation to calculate the heat flux density since we could as well use the FE simulation to directly compute the temperature difference and thermal resistance between junction and case.

In the author's view the effective heat spreading concept serves two purposes. On the one hand it provides a clear definition of heat spreading cone and spreading angle which so far is often based on a somewhat vague idea of how the heat is spread inside a structure. Heat spreading cone and angle can be visualized which helps us to gain insight into spreading mechanism and influencing factors. Looking at figure 3 we see *e.g.* that the popular assumption of a 45° spreading angle is overly optimistic in that case. This is the educational aspect.

On the other hand the effective heat spreading concept also serves a practical purpose. As shown in [5] we can often find generally applicable rules for the effective spreading angle which are valid not only for one particular case/device but provide a

Figure 4: Discretization of the effective heat spreading cone.

good approximation for a whole sub-class of cases (*e.g.* all power semiconductors with solder die attach). Based on these rules and *Equation* (5) we can implement more accurate spreadsheet calculators for the thermal resistance of this sub-class of devices.

### **FINAL REMARK**

We could also try to define the spreading cone by a surface that intersects all isothermals at 90° angle thus ensuring zero heat flux across that border. But contrary to the approach presented above the resulting heat spreading cone would be useless when it comes to computing the associated thermal resistance since the heat flow density over parallel cross sections of the spreading cone is not constant.

#### REFERENCES

1. Clemens J.M. Lasance, "Heat Spreading – Not a trivial Problem", *Electronics Cooling*, Vol. 14, No. 2, May 2008.

2. Bruce Guenin, "The 45° Heat Spreading Angle – An Urban Legend?", *Electronics Cooling*, Vol. 9, No. 4, Nov. 2003.

3. Yasushi Koito, Shoryu Okamoto, and Toshio Tomimura, "Two dimensional numerical investigation on applicability of 45° heat spreading angle", *Journal of Electronics Cooling and Thermal Control*, Vol. 4, pp. 1-11, 2014.

4. Seaho Song, Seri Lee, and Van Au, "Closed-Form Equations for Thermal Constriction/Spreading Resistances with Variable Resistance Boundary Condition," *IEPS Conference*, pp. 111-121, 1994.

Dirk Schweitzer and Liu Chen, "Heat Spreading Revisited – Effective Heat Spreading Angle", *Proc. 31st SEMITHERM*, San Jose, pp. 88-94, 2015.

### **On-site Cogeneration for Reducing Data Center Primary Energy Use**

By Dustin W. Demetriou IBM

### INTRODUCTION

**S MOST READERS ARE AWARE**, the data center industry has put an increased focus on energy efficiency and environmental impact. Data centers in the United States are estimated to consume nearly 2% of the total electricity. The *de facto* metric used in the data center industry to evaluate energy efficiency has been the Power Usage Effectiveness (PUE), as defined by The Green Grid [1]. As defined by *Equation (1)*, PUE is the ratio of the total power that enters the data center facility (including cooling, power distribution losses, lights, HVAC, IT Equipment, etc.) to the power provided to the IT equipment.

$$PUE = \frac{Total Facility Power}{IT Equipment Power}$$

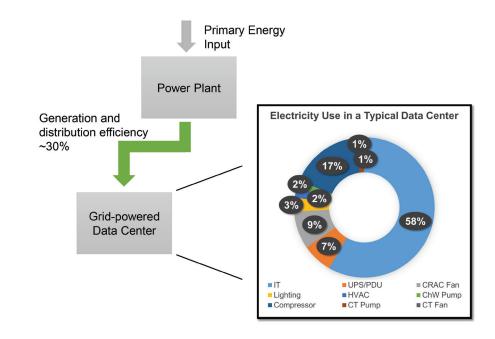

Recent surveys [2, 3] have shown that the average data center PUE is still greater than 1.7. This means that for every 1.0 watt of IT Equipment power, another 0.7 watts are needed to deliver power and cooling. An example breakdown of the power use in a data center is shown in Figure 1. This example data center has a PUE of 1.71.

**Dustin W. Demetriou, PhD** is an Advisory Engineer at IBM Corporation in the IBM Systems' Advanced Thermal Energy Efficiency Lab focusing on advanced cooling technologies, cross brand thermal development and state-of-the-art data center designs. He received a Ph.D. in Mechanical and Aerospace Engineering from Syracuse University. His research is focused on the analysis, application and optimization of energy conversion systems, particularly in the area of high-density data centers and high-performance buildings and the development of advanced cooling technologies for IT hardware. He has authored or coauthored a number of journal and peerreviewed conference publications in the areas of building simulation and energy efficient data centers. His work has been awarded numerous honors, including the All-University Doctoral Prize at Syracuse University, ASME Journal of Electronics Packaging Best Paper Award, ASME InterPACK best paper in Data Centers and Energy Efficient Electronic Systems and the best in Mechanical and Aerospace Engineering from Syracuse University and a BS in Mechanical Engineering from Manhattan College.

(1)

The PUE only accounts for the power distributed throughout the data center. In almost all cases, this electricity is generated and delivered to the data center from a remote power plant. The actual primary energy required ( $Q_{PE}$ ) to operate the data center is given by:

$$\dot{Q}_{PE} = \frac{P_{IT} \times PUE}{\eta_{th} \times \eta_{dist}} \tag{2}$$

The efficiency in the denominator of *Equation (2)* is the combination of the power plant's thermal efficiency  $(\eta_{th})$  and the efficiency of transmitting and distributing the power  $(\eta_{dist})$  from the site of generation to the data center. The US Department of Energy and Energy Information Administration have reported that these distribution losses are typically about 7% [4].

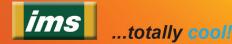

### USING ON-SITE POWER GENERATION FOR DATA CENTERS

An on-site power generation system for a data center, as shown in *Figure 2*, provides a number of advantages compared to a grid-powered data center. For example, an on-site power generation system allows the use of the generator's waste energy to provide cooling using a thermally-activated absorption chiller [5], otherwise known as a cogeneration system. Unlike many commercial buildings, a data center can provide a

Figure 1: Energy Flow for a Conventional Grid-Powered Data Center.

high utilization of the cogeneration system's thermal output because its electrical and thermal demands are strongly correlated. Every watt of electrical power provided to the data center must be thermally removed. The use of an absorption chiller to provide cooling removes a substantial electricity demand due to the elimination of mechanical cooling.

To determine a PUE for a cogeneration system based data center, we can remove both the HVAC (heating, ventilating, and air conditioning) and compressor loads - as these are provided by the absorption chiller using the data center's

waste heat, with substantial reduction in electricity consumption. Additionally, the cooling tower pump and fan power requirements must scale accordingly since the absorption chiller coefficient of performance (COP) is much lower than a conventional vapor compression chiller. The condenser load on the chiller ( $Q_{CND}$ ) can be computed as:

$$\dot{Q}_{CND} = \dot{Q}_{EVAP} \left( 1 + \frac{1}{COP} \right) \tag{3}$$

where,  $Q_{EVAP}$  is the evaporator load, which includes the

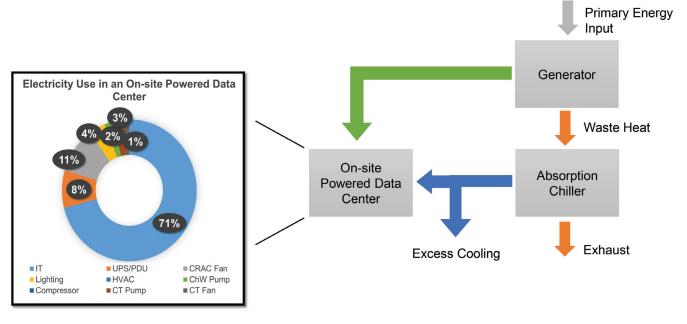

### Now You Can Cool Your Electronic Devices at the Component Level

Get to know the ThermaBridge<sup>TM</sup> from *ims*. The ThermaBridge<sup>TM</sup> is *ims*' unique solution for the removal of unwanted heat from electrical circuitry. While the ThermaBridge<sup>TM</sup> excels at moving heat, it is electrically isolated. Unlike copper strips, it can be used anywhere regardless of voltage potential and has no electrical effect on circuit performance. And it works at the *component* level.

- Thermally conductive

- Electrically isolated

- Component level solution

Contact *ims* or your local *ims* rep today! www.ims-resistors.com/ec.html

ThermaBridge<sup>TM</sup> Thermal Transfer Device

Resistors • Attenuators • Terminations • Splitters Couplers • Dividers • Filters • Thermal Transfer Devices

International Manufacturing Services, Inc. 50 Schoolhouse Lane Portsmouth, RI 02871 USA Tel:1.401.683.9700

Figure 2: Energy Flow for an On-Site Powered Cogeneration Data Center.

IT power, uninterruptable power supply (UPS) and power distribution unit (PDU) losses, lighting, HVAC and chilled water pumps. The corresponding cooling tower pump power in the cogeneration system can be estimated by scaling the cooling tower pump power in the conventional data center, as observed in *Equation (4)*:

$$P_{CT,pump}^{CG} = P_{CT,pump} \frac{\dot{Q}_{CND}^{CG}}{\dot{Q}_{CND}}$$

(4)

Similarly, the cooling tower fan can be scaled based on the condenser load. The corresponding PUE for a cogeneration system based data center, as shown in *Figure 2*, is 1.41. There are many other benefits to generating power on-site that can further reduce the PUE, including water cooling and DC power distribution. These are discussed in more detail in [6].

### PRIMARY ENERGY REQUIREMENT OF A COGENERATION SYSTEM DATA CENTER

While PUE can be computed for a cogeneration system based data center, it does not highlight the complete picture when the generator waste heat is used to provide cooling for the data center. Instead, we will focus on the primary energy required for a data center that utilizes a cogeneration system, as described in [6], compared to a traditional grid-powered data center. Referring to *Figure 2*, the generator, which could be a turbine, gas generator, or fuel cell, has a thermal efficiency  $(\eta_{th}^{\text{EN}})$  defined as:

$$\eta_{th}^{GEN} = \frac{P_{IT} \times PUE^{CG}}{\dot{Q}_{PE}^{CG}}$$

(5)

where the product of the IT power and the PUE is the work output of the generator.

The absorption chiller has a thermal coefficient of performance ( $COP_{th}$ ) defined as,

$$COP_{th} = \frac{\dot{Q}_c}{\varphi \dot{Q}_{ex}} \tag{6}$$

where  $Q_c$  is the cooling load,  $Q_{ex}$  is the exhaust energy from the generator, and  $\phi$  is a waste heat recovery factor. The recovery factor is a function of the effectiveness and dew point temperature limits of the absorption chiller and describes the fraction of useable waste heat.

The first law of thermodynamics applied to the generator states that:

$$\dot{Q}_{ex} = \dot{Q}_{PE}^{CG} - P_{IT} \times PUE^{CG} \tag{7}$$

By combining *Equations* (5), (6) and (7), the cooling output of the absorption chiller can be computed as:

$$\dot{Q}_{c}^{CG} = \varphi COP_{th} \frac{P_{IT} \times PUE^{CG}}{\eta_{th}^{GEN}} \left(1 - \eta_{th}^{GEN}\right)$$

(8)

As shown in *Figure 2*, part of this cooling is used to cool the data center. However, depending on the generator thermal efficiency, excess cooling  $(Q_{c,excess}^{CG})$  may be available to use for other cooling loads, such as a nearby campus building. The amount of excess cooling available is:

$$\dot{Q}_{c,excess}^{CG} = \dot{Q}_{c}^{CG} - \dot{Q}_{EVAP}^{CG}$$

(9)

## **Cooling Solutions** FOR ALL THERMAL CHALLENGES

**Aavid Thermalloy** provides the widest array of innovative thermal management solutions and engineering services for any industry.

Die

Casting

Heat

**Pipes**

Fans

Custom

Designs

Liquid

Cooling

**PulseJets**<sup>™</sup>

Heat

Sinks

Thermal

Interface

**Materials**

#### **NEW! Aavid Gap Filler Interface Materials**

These premium interface materials offer extremely high thermal conductivity without sacrificing compliancy and flexibility. These attributes combined with a variety of adhesion, thickness and size options allow Aavid's Gap Fillers to boost the performance of any design!

Aavid has recently launched its new line of gap filler pads and sheets!

### Aavid PulseJets<sup>™</sup>

Aavid PulseJets™are unique frictionless air movers that utilize entrainment and turbulent air flow to provide concentrated, reliable cooling in small form factor designs. These low profile coolers deliver quick, jet-like bursts of air across heat sources; and when combined with a heat sink, they can offer over three times the heat transfer of passive cooling.

Introducing: RazorJets™

Now available: Dual Cool Jets

### 1.855.322.2843 | WWW.AAVID.COM

In a conventional data center, this excess cooling would need to be provided by an electric vapor compression chiller. The primary energy that would be required to generate this excess cooling in a grid-power arrangement is given by:

$$\dot{Q}_{c,offset} = \frac{Q_{c,excess}^{CG}}{COP_e \times \eta_{th} \times \eta_{dist}}$$

(10)

where  $\text{COP}_{e}$  is the coefficient of performance of the electric vapor compression chiller.

Therefore, the net primary energy for the cogeneration system data center is given by subtracting the offset, *Equation* (10), from the primary energy required by the cogeneration system, *Equation* (5).

### EXAMPLE OF AN ON-SITE POWERED DATA CENTER COMPARED TO A CONVENTIONAL GRID POWERED DATA CENTER

To highlight the energy savings of an on-site power generation system, we can use *Equations* (5) through (10) and the data center PUE as shown in *Figures 1* and 2 for the conventional and cogeneration data center, respectively, to compare the primary energy required. We can show this as a percentage savings of the cogeneration system. *Table 1* gives the parameters used in the analysis.

| Thermal efficiency, $\eta_{\text{th}}$                   | 33%  |

|----------------------------------------------------------|------|

| Distribution efficiency, $\eta_{\text{dist}}$            | 93%  |

| Electric Coefficient of<br>Performance, COP <sub>e</sub> | 4.88 |

| Thermal Coefficient of<br>Performance, COP <sub>th</sub> | 1.20 |

| Waste heat reuse factor, $\phi$                          | 58%  |

**Table 1:** Parameters used in example analysis of an on-site power data center.

Values represent typical values for commercially available equipment.

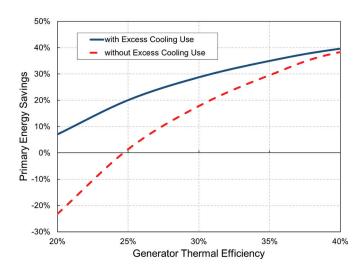

*Figure 3* plots the primary energy savings of the cogeneration system data center versus the generator thermal efficiency. The solid line shows the savings when the cogeneration system's excess cooling can be fully utilized, both to cool the data center and an additional cooling load. The dashed line shows the case where the absorption chiller cooling can only be used to cool the data center. This would be the case if the data center was isolated. It can be seen that compared to a grid-powered data center, with an overall 30% efficiency (generation + distribution), without being able to use the excess cooling, the on-site power system offers little to no advantage until the generator efficiency reaches greater than 25%. Many

Figure 3: Primary Energy Savings for the Example Cogeneration-based Data Center.

commercial microturbines can now offer thermal efficiencies nearing 28% [7]. When the excess cooling can be used, these systems can provide substantial primary energy savings, in excess of 20%.

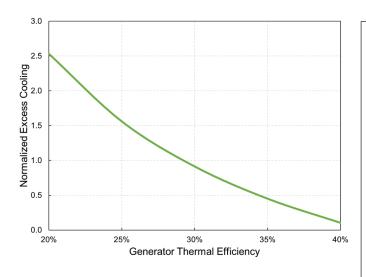

As the generator thermal efficiency increases, the amount of primary energy necessary to provide the required data center power decreases, as shown by *Equation (5)*. By the first law of thermodynamics, this also means that less exhaust energy will be available to generate cooling in the absorption chiller. Figure 4 plots the excess cooling, which has been normalized by the data center power, versus the generator thermal efficiency. As the generator efficiency reaches 40%, which may be representative of a large gas generator or a stationary fuel cell, the excess cooling approaches zero. This means that the waste heat from the generator can be used to provide just enough cooling for the data center. Referring back to *Figure 4*, the higher the generator thermal efficiency, the more primary energy savings of an onsite power generation system. Additionally, when the generator efficiency nears 40%, the data center needs to rely less on having an additional nearby source to utilize the excess cooling, as seen by the solid and dashed lines converging.

### CONCLUSIONS

This article showed how a simple thermodynamic analysis can be effectively utilized to analyze alternative power and cooling options for data centers. It highlighted the benefits of on-site cogeneration for data center applications, where the thermal and electric demands are strongly correlated. The article also described a primary energy methodology that shows the benefits of an on-site system compared to a traditional grid-powered data center.

### REFERENCES

[1] ASHRAE, 2014. *PUE: A Comprehensive Examination of the Metric,* ASHRAE Datacom Series 11.

Figure 4: Data Center Excess Cooling Available for the Example Cogeneration System Data Center.

[2] Stansberry, M, "2014 Data Center Industry Survey," <u>https://journal.</u> <u>uptimeinstitute.com/2014-data-center-industry-survey/</u>, last retrieved on August 24, 2015.

[3] Salim, M. and Tozer, R., 2010, "Data Centers' Energy Auditing and Benchmarking- Progress Update," ASHRAE Transactions, Vol. 116(1), pp. 109 - 117.

[4] Energy Information Administration (EIA), 2010, Electric Power Monthly, September 2010. Energy Information Administration, US Department of Energy, Washington DC.

[5] Herold, K.E., Radermacher, R., and Klein, S.A., Absorption Chillers and Heat Pumps, CRC Press, 1996.

[6] Erden, H.S. and Khalifa, H.E., 2012, "Energy and environmental assessment of On-site power and cooling for data centers," HVAC&R Research, Vol. 18(1-2), pp. 51-66.

[7] U.S. Environmental Protection Agency, 2015, "Section 5. Technology Characterization - Microturbines," Catalog of CHP Technologies, <u>http://www.epa.gov/chp/technologies.html</u>, last retrieved on August 24, 2015.

Providing creative solutions to improve the reliability of electronics equipment

Jones Tech LLC 19925 Stevens Creek Blvd., Suite 100 Cupertino, CA 95014, USA

Sales@jones-corp.com www.jones-corp.com

Thermal Pad • Thermal Gel • Thermal Grease Phase Change Material • Pyrolytic Graphite

| Greek Symbols |                         | Nomenclature |                            |

|---------------|-------------------------|--------------|----------------------------|

| η             | Efficiency              | СОР          | Coefficient of Performance |

| arphi         | Waste heat reuse factor | Р            | Power, kW                  |

| Superscrip    | ts                      | PUE          | Power Usage Effectiveness  |

| CG            | Cogeneration            | Q            | Energy, kW                 |

| GEN           | Generator               |              |                            |

| Subscripts    |                         |              |                            |

| с             | Cooling                 |              |                            |

| CND           | Condenser               |              |                            |

| СТ            | Cooling tower           |              |                            |

| dist          | Distribution            |              |                            |

| е             | Electric                |              |                            |

| EVAP          | Evaporator              |              |                            |

| ex            | Exhaust                 |              |                            |

| IT            | Information technology  |              |                            |

| ΡΕ            | Primary energy          |              |                            |

| th            | Thermal                 |              |                            |

Note: The above are symbols included in this article.

# **Cooling Matters**

News of thermal management technologies

### AIR FORCE INQUIRES ABOUT THERMAL MGMT.SOLUTIONS FOR FUTURE AIRCRAFT

**8/11/15** - The U.S. Air Force is looking into new thermal management techniques to cool the electronics in future fighter aircraft.

"Officials of the Air Force Research Laboratory at Wright-Patterson Air Force Base, Ohio, issued a broad agency announcement Friday (BAA-AFRL-RQKP-2015-0002) for the Hybrid-Cycle Power and Thermal Management System (PTMS) project," according to Military & Aerospace Electronics.

"The Air Force Research Lab's Power and Control Division, Mechanical & Thermal Systems Branch are asking industry for electronics cooling ways to blend air-cycle cooling, vapor-cycle cooling, chilled fuel, and other thermal energy storage mechanisms to keep electronics cool on future jet fighters," according to researchers.

Source: Military & Aerospace Electronics

### 3D WHITE GRAPHENE YIELDS FAN-FREE COOLING/THERMAL MANAGEMENT SOLUTIONS

**7/20/15** - Researchers from Rice University have discovered that 3D White Graphene could help cool small-scale electronic devices by itself.

When the research group completed simulations of heat flows through 3D white graphene structures, which are made of boron nitride, the normal 2D structure took the form of normal hexagonal structure of graphene. The team then investigated "how its natural heat conduction properties could be exploited in 3D arrangements."

"Simulations show that 3D structures of white graphene-sheets of the 2D stuff held together with boron nitride nanotubes- quickly move heat in all directions. But they also show that by tuning the lengths and densities of the interconnecting tubes, the material can be tuned to channel heat in specific directionsshorter ones slow conduction, while longer ones speed it up," according to Gizmodo.

Even though the team's research is solely based on simulations, they remain positive that this discovery will help introduce new kinds of 3D thermal management systems for small electronic devices in the near future.

### CALIFORNIA ENERGY CODE UPDATED; NEW REGULATIONS FOR COOLING DATA CENTERS

**7/28/15** - The California Energy Code, also known Title 24 of the CA Code of Regulations – part 6, has been revised. The new revision implements new regulations for cooling data centers and server rooms in order to improve efficiency, reduce daily operation costs, reduce carbon footprints and simplify cooling models.

The new rules apply to computer rooms, which Title 24 defines as: "A room whose primary function is to house electronic equipment and that has a design equipment power density exceeding 20watts/ft<sup>2</sup> (215 watts/m<sup>2</sup>) of conditioned floor space."

The new requirements affect the way data centers are cooled. The new CA Title

24 Code Requirements include: economization, airside economization, waterside economization, reheat prohibited, humidification, fan efficiency, fan control and air containment.

> Source: Datacenter Journal

Source: Gizmodo

### Datebook

**SEPTEMBER 15-17**

Electric & Hybrid Vehicle Technology Expo

NOVI, MICHIGAN, U.S. www.evtechexpo.com

### SEPTEMBER 16-19

LED China 2015 SHANGHAI, CHINA www.chinaexhibition.com

### **SEPTEMBER 22-24**

LED Professional Symposium & Exhibition 2015

FESTSPIELHAUS BREGENZ, AUSTRIA

www.heatmanagement.com/en/ announcements/events

### SEPTEMBER 22-24

Advanced Technology Workshop and Tabletop Exhibit on Thermal Management LOS GATOS, CALIF., U.S.

LOS GATOS, CALIF., U.S. www.imaps.org/thermal

### LEDS TO MOVE DATA FASTER IN ELECTRONICS

8/4/15 - University of Virginia engineering researchers have come up with a way for LEDS to move data to wireless devices faster.

This process involves "using light waves from light-emitting diode fixtures to carry signals to wireless devices at 300 megabits per second from each light. It's like having a whole wi-fi system all to yourself; using light waves, there would be more network access points than with radio waves, so less sharing of the wireless network," according to researchers.

"Visible light communications has the potential to significantly increase the speed of Internet connection in multiuser indoor environments due to the broad bandwidth of the visible light. It will offer a huge energy saving for the nation since energy is already used for lighting, and thus does not need to be expended for communications," the team concluded.

Source: Phys.org

### **NEW MATERIAL DECREASES ENERGY USAGE IN ELECTRONICS**

8/4/15 - Researchers have determined that gallium nitride (GaN) could become the next best semiconductor for electronics because it would immensely cut energy usage.

Cambridge Electronics Inc. (CEI) has announced a new line of GaN transistors and power electronic circuits. This line promises to reduce energy usage by 10 to 20 percent in consumer electronics, data centers and electric cars by 2025.

CEI plans to use these transistors to make data centers use less energy, electric cars more powerful and cheaper to build and power adapters one-third of the size, according to Phys.org.

Source: Phys.org

### **3D SHAPES FORMED FROM FLAT** SHEFTS OF GRAPHENE

3/9/15 - A team from the University of Illinois at Urbana-Champaign has developed a new method for forming 3D shapes from flat 2D sheets of graphene. This development will pave the way for flexible electronics and integrated systems that are graphene and MEMS hybrid devices.

Integrating 2-D graphene sheets onto 3D structured surfaces allows the graphene to

ture: however. the 3D features and dimensions vary from 3.5 to 50 um.

**Science Daily**

### HPC NETWORKS SUCCESSFUL LIQUID COOLED FOR FIRST TIME

7/20/15 - Icetope, a company that specializes in the liquid cooling of electronics, announced it has successfully liquid cooled HPC networks.

"Liquid cooling systems work by transferring all the heat directly into liquid. The waste heat is then removed in the form of hot water, which is pumped around the cabinet and can

> be re-purposed for domestic heating," according to Elec-tronics Weekly.

The company developed a "fan-less Mellanox-based InfiniBand and Ethernet network and interconnect switch for supercomputer (HPC) systems."

Source: Electronics Weekly

**DECEMBER 7-10**

Gartner Data Center.

**Infrastructure &**

Conference

**Operations Mgmt.**

### SEPTEMBER 29-31

SAE 2015 Thermal Management Systems Symposium TROY, MICH., U.S.

http://saeevents.org

### **OCTOBER 6-8**

**THERMAL LIVE 2015** ONLINE http://thermallive2015.com

THERMAL LIVE

### **OCTOBER 27-30**

Hong Kong International Lighting Fair HONG KONG, CHINA www.hktdc.com

LAS VAGAS, NV, U.S. www.gartner.com/events

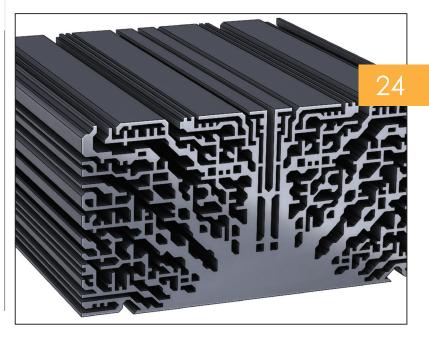

### An Additive Design Methodology for Heatsink Geometry Topology Identification

**Robin Bornoff and John Parry** Mentor Graphics Corporation

#### INTRODUCTION

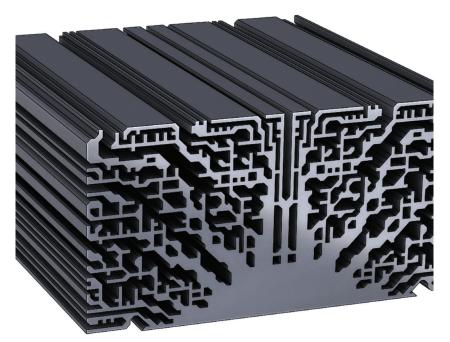

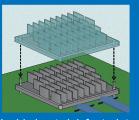

**STABLISHED HEATSINK** manufacturing processes such as extrusion, casting and milling constrain the achievable topology and geometry of the heatsink. The advent of metallic 3D printing (additive manufacture) processes such as selective laser melting (SLM) may remove many of these constraints, forcing the designer to reconsider the approach taken to determine a thermally-efficient heatsink design.

Classic heatsink design involves considering a parametrically specified heatsink topology then optimising those parameters to meet thermal, weight and cost constraints. Those parameters for example might be base thickness, number of fins, fin thickness, fin spacing, and/or fin height. In many ways it is the manufacturing process that dictates those parameters and by how much they can vary. So, how might a heatsink design process be performed if those constraints are no longer imposed?

An additive design methodology has been developed by the Authors that allows a non-parametric topology of the heatsink to be identified as part of an iterative simulation-based process. At its heart, the additive design methodology involves inspection of the performance of an initial design, a determination of where that

**Robin Bornoff** achieved his Mechanical Engineering Degree from Brunel University in 1992. He was awarded a Ph.D. from Brunel University in 1995 for CFD research. He joined Mentor Graphics Corporation, Mechanical Analysis Division (formerly Flomerics Ltd) after his Ph.D. as an application and support engineer, specializing in the application of CFD to electronics cooling and the design of the built environment. Bornoff has served as the Product Manager responsible for the FloTHERM, FloVENT and FloTHERM PCB software. He is currently Market Development Manager.

**John Parry**, a chemical engineer by training, got involved with CFD more than 30 years ago, joining Flomerics Ltd. when it founded in 1989, coordinating EC-funded and other projects and overseeing the technical integration of MicReD into the company. Now part of Mentor Graphics, John is the Mechanical Analysis Division's Electronics Industry Manager. Parry's technical contributions include developing compact thermal models for fans, heat sinks, chip packages and LEDs, co-inventor of BottleNeck and ShortCut numbers, and applying Design of Computer Experiments and optimization techniques. He serves on the JEDEC JC15 and various conference committees.

design should be minimally modified. The modification is then made, and the performance re-evaluated. This process is repeated until a design criterion is met.

This is a subset of a methodology that would entail a minimal improvement made at every possible location, the most advantageous improvement implemented and the process repeated. This in turn is a subset of a methodology that would entail every possible topology being simulated and the best one identified. The present approach aims to be tractable in terms of (simulation) time whilst still having the flexibility to identify an application-specific topology, and is an application of Bejan's Constructal Law [1], which states:

"For a finite-size system to persist in time (to live), it must evolve in such a way that it provides easier access to the imposed currents that flow through it."

Such a law can be said to underpin the formation of many systems both animate and inanimate, including, but not limited to, the branching nature of lightning, rivers, lungs and trees. Various studies based on the Constructal law have focused on "volume to point" (VP) flow systems: thermal conduction of heat [2], liquid flow in a porous media [3] and air flow in lungs [4].

Heatsink behaviour is also a VP problem, though taken as a volume of "cold" used quench a point (rather a small area) heat source. It is not surprising that there are analogies between heatsinks and, say, trees. The heatsink

Figure 1: Initial steps of the additive design process.

base, like the tree trunk, enables that which is to flow (heat in a heatsink, liquid in a tree) to pass to the area extending portion of it. The heatsink fins, like branches and leaves of a tree, then transfer what is flowing out to their ambient.

The Constructal law can be seen in action in the organic growth exhibited by the additive design methodology

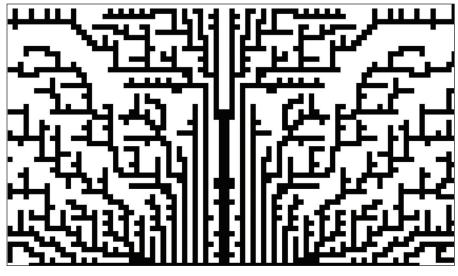

Figure 2: Heatsink profile after one 'year' of growth.

Figure 3: Forced convection heatsink profile after three 'years' of growth.

reported in this article, which is abstracted from Reference [5].

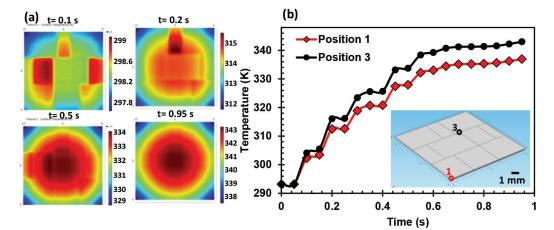

### APPLICATION TO A FORCED CONVECTION COOLING ENVIRONMENT

When applied to heatsink design the additive design process starts by considering the thermal performance of a thin section of heatsink base placed on a heat source, a key from which the heatsink geometry may evolve. This initial geometry is simulated in a cooling environment and the maximum surface temperature location identified. It is postulated that an improvement in the thermal performance of the heatsink can be achieved by increasing the surface area at the point of highest temperature. To achieve this, an additional piece of heatsink material geometry is added to the heatsink, on that face,

and the modified heatsink geometry re-simulated. For this study a forced convection cooling environment is used and a 1mm x 1mm full length rib is chosen as the additive geometric shape. The first 5 steps in the additive design process are shown in Figure 1. The heatsink design space is 100mm x 100mm x 50mm. There is allowance for 25mm of bypass on the top and the two sides of the heatsink. The initial heatsink base geometry fills the design space in the flow direction, covers the heat 30mm x 30mm heat source in the spanwise direction, is 1mm thick and has a thermal conductivity of 205 W/m-K. The inflow is set to 3m/s with an ambient pressure condition at the outlet.

There is no guarantee that the addition of geometry at the hottest point will always cause a decrease in heatsink thermal resistance. If a geometry ad-

Figure 4: Final chamfered additively designed forced convection heatsink.

dition is made that causes an increase in thermal resistance then that added geometry is removed and the location marked so as not to be considered again during the growth process. The growth process concludes when the heatsink has grown to fill a defined design volume and there are no locations left to extend the geometry so as to improve the thermal performance. We define this as the first "year" of growth. A front view of the geometry after this first year of growth is shown in *Figure 2*. Note that symmetry was assumed for the computational fluid dynamics (CFD) simulations.

A subsequent second year of growth was allowed by resetting all those geometry addition locations that had caused an increase in the thermal resistance of the heatsink during the first year. Some of those locations of area extending that had proved to be detrimental initially, proved to be highly advantageous in this second year of growth. Specifically closer to the heat source where the second year of growth saw a thickening of the base so as to facilitate the flow of heat to the now large surface area (but thin cross section) branched fins.

This resetting and continued growth was repeated for a third "year", after which no subsequent year of growth provided any further improvement in thermal performance and the additive design process was ended. The final heatsink topology is shown in *Figure 3*.

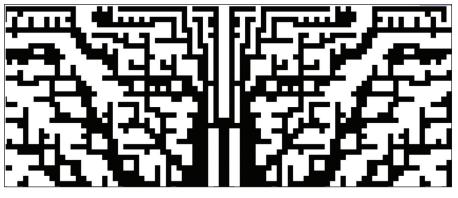

An evident deficiency of the use of a square section rod to grow the geometry is that any angled or curved topological features that manifest will have stair-stepped edges. Although it could be argued this might increase heat transfer, it may be offset by the increase in surface friction. A smoothing stage is therefore conducted where the stepped angled sections are (manually) chamfered (Figure 4). This results in a slight (1.8%) improvement in thermal performance.

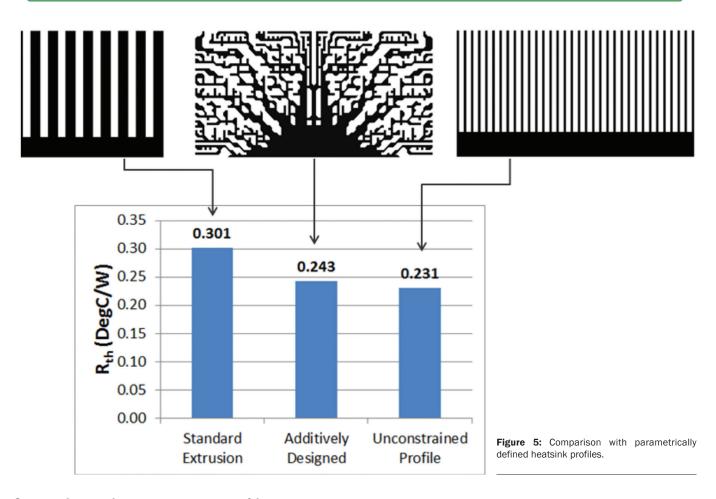

### COMPARISON TO PARAMETRICALLY DEFINED HEATSINK PROFILES

It was neither the intention nor the outcome of this study to demonstrate a superior thermal performance of an additively designed heatsink compared to more classic heatsink topologies. However, to put the thermal performance of the additively designed heatsink into perspective, it is compared to two other heatsinks with parametrically definable topologies.

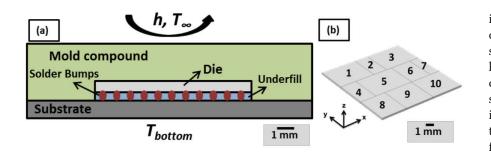

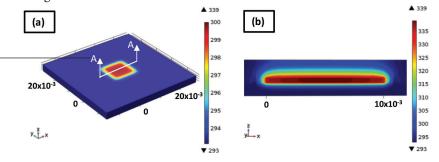

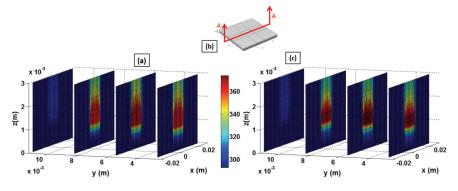

A standard extrusion will have manufacturing constraints such as the maximum aspect ratio of each fin (and similarly fin gap) and minimum fin width. A maxi-