AN INEXPENSIVE MULTI-CHANNEL AC HEATER CONTROL SYSTEM

# Electronics COOLING

SEPTEMBER 2014

CVD DIASMOS INTEGRATING A SUPERIOR

INTEGRATING A SUPERIOR THERMAL MATERIAL

### Bergquist Highly Engineered Liquids Give You Complete Flexibility Over The Design And Delivery Of Your Thermal Solutions.

### Bergquist's full line of liquid polymers make it easy to customize your material, pattern, volume and speed.

Bergquist's advanced liquids are specifically designed to support optimized dispensing control with excellent thermal conductivity. Dispensed in a liquid state the material creates virtually zero stress on components. It can be used to interface and conform to the most

intricate topographies and multi-level surfaces. They are thixotropic in nature, helping the material to remain in place after dispensing and prior to cure. Unlike pre-cured materials, the liquid approach offers infinite thickness options and eliminates the need for specific pad thicknesses for individual applications.

Whether automated or hand dispensed, Bergquist liquid materials have natural tack and precisely flow into position for a clean final assembly with little or no stress on components.

### Less stress, reduced application time with minimal waste.

Either manual, semi-automatic or automated dispensing equipment offers precise placement resulting in effective use of material with minimal waste. Boost your high volume dispensing needs by capitalizing on our expertise. Bergquist can help customers optimize their delivery process through its unique alignment with several experienced dispensing equipment suppliers.

### Visit us for your FREE liquid samples.

Take a closer look at the Bergquist line of liquid

dispensed materials by getting your FREE sample package today. Simply visit our website or call us directly to qualify.

Request your FREE Liquid TIM Dispensed Sample Card

Call **I.800.347.4572** or visit www.bergquistcompany.com/liquiddispense

18930 West 78th Street • Chanhassen, MN 55317 • TS 16949 Certified (800) 347-4572 • Phone (952) 835-2322 • Fax (952) 835-0430 • www.bergquistcompany.com

# **CONTENTS**

2 EDITORIAL

Peter Rodgers, Editor-in-Chief, September 2014

4

### **COOLING MATTERS**

Spin Waves Transport Heat in Insulating Materials; Superconducting Refrigerator Cools via Tunneling Cascade; and more

6

### **THERMAL FACTS & FAIRY TALES**

Virtual Prototyping

Peter Rodgers, The Petroleum Institute

10

### **TECHNICAL BRIEF**

An inexpensive multi-channel AC heater control system

**Lucien François Dorthe and Paul Kolodner**Bell Laboratories, Alcatel-Lucent, Inc.

14

### **CALCULATION CORNER**

Estimating the Thermal Interaction between Vertically Stacked Chips in a Multi-Chip Package

Je-Young Chang, Ashish Gupta, Intel Corporation

# CVD DIAMOND INTEGRATING A SUPERIOR THERMAL MATERIAL Thomas Obeloer, Bruce Bolliger, Element Six

### **FEATURED ARTICLES**

18

HIGH HEAT FLUX, SINGLE-PHASE

MICROCHANNEL AND MINICHANNEL COOLING

WITH WATER AND LIQUID METAL

**Rui Zhang¹, Marc Hodes¹, Nathan Lower² and Ross Wilcoxon²** Rockwell Collins², Tufts University¹

28

### **JET IMPINGEMENT ON MICRO PIN FINS**

Sidy Ndao, University of Nebraska-Lincoln

30

**INDEX OF ADVERTISERS**

# **Editorial**

# The Need for Electronics Thermal Design Practices to Embrace Sustainability

Peter Rodgers, Editor-in-Chief, September 2014

by 36% from 2010 to 2030, driven by population and economic growth in developing nations. This demand growth, combined with the depletion of fossil energy resources and the consequent escalation in energy prices, as well as environmental and energy security concerns, have motivated increased attention to sustainability. Despite progress in renewable energy conversion, the latest global economic recession has however prompted nations to refocus on conventional energy sources (e.g., fossil), albeit in a more sustainable way than in the past.

In relation to a previous 2008 editorial titled "en Route to a Greener Thermal Technology" [1], the question was posed "What can thermal engineers do to facilitate this change?" Suggestions included (i) adopting a holistic view of energy consumption, so that we all understand the true energy costs associated with performing tasks demanded by modern life, and (ii) contribute to the development of electronics-based technologies that are energy efficient, not only at the device level, but also at the system and societal level. Both points are touched upon in this article, to evaluate current progress in these areas. Before doing so, let's consider two simple statistics regarding present days' magnitude of electronics energy usage:

- Since 2010, the electricity consumption of the global data center industry has risen from 1.3% to approximately 3% in 2014, with almost half of this power used for cooling the electronics

- When accounting for wireless connections, data usage and battery charging, an average iPhone consumes 361 kWh each year, which exceeds the power consumption of a medium-sized, energy-efficient refrigerator.

To date, thermal design optimization has rarely been driven by energy outcomes, but rather by tradeoff between product electrical, thermal-hydraulic performance and non-holistic economic figures. This is in spite of well-known energy conservation metrics developed for electronics thermal management over the last two decades. With the objectives to reduce the material and energy consumption rates associated with the cooling of microelectronic equipment, design optimization methodologies focusing on least-energy, entropy generation minimization, and exergy efficiency have long been proposed. Such metrics permit the cost and environmental impact associated with energy consumption to be evaluated, and are widely used in energy-intensive industries (e.g., cement, steel, chemical, petrochemical). In those sectors, these metrics have led to the adoption of waste heat recovery technologies, which have resulted in substantial economic and environmental gains.

Unfortunately, the potential of these design methodologies is hardly exploited in today's electronics thermal design environments, with the recent exception of data centers. The extension of these design strategies to other electronic applications now needs to be considered. Technologies for recovery of low-grade heat are emerging, including:

- Conventional and nanocomposite thermoelectric devices for electrical power generation

- · Phase change materials for energy storage

- Chip-level combined heat and power (CHP)

- Semiconducting materials for conversion of heat into electron-spinning energy Sustainability will play an increasingly important role in the thermal optimization of electronic systems in the future. To accelerate the "en Route to a Greener Thermal Technology," ultimately new regulations will require to be established that will place greater constraints on the consumption of energy by electronic systems.

### **REFERENCE**

[1] Guenin, B., 2008, "en Route to a Greener Thermal Technology" Electronics Cooling, Vol. 14, No. 1, pp. 1.

# Electronics **COOLING**

www.electronics-cooling.com

### **ASSOCIATE TECHNICAL EDITORS**

Bruce Guenin, Ph.D. Principal Hardware Engineer, Oracle bruce.guenin@oracle.com

Madhusudan Iyengar, Ph.D. Thermal Engineer, Google miyengar@gmail.com

Peter Rodgers, Ph.D. Professor, The Petroleum Institute prodgers@pi.ac.ae

Jim Wilson, Ph.D., P.E. Engineering Fellow, Raytheon Company jsw@raytheon.com

#### **PUBLISHED BY**

ITEM Media 1000 Germantown Pike, F-2 Plymouth Meeting, PA 19462 USA Phone: +1 484-688-0300; Fax:+1 484-688-0303 info@electronics-cooling.com; electronics-cooling.com

#### **CONTENT MANAGER**

Belinda Stasiukiewicz bstas@item-media.net

#### **BUSINESS DEVELOPMENT MANAGER**

Casey Goodwin cgoodwin@item-media.net

#### **GRAPHIC DESIGNER**

Evan Schmidt eschmidt@item-media.net

### **ASSISTANT EDITOR**

Aliza Becker abecker@item-media.net

### **PRESIDENT**

Graham Kilshaw gkilshaw@item-media.net

### REPRINTS

Reprints are available on a custom basis at reasonable prices in quantities of 500 or more. Please call +1 484-688-0300.

### **SUBSCRIPTIONS**

Subscriptions are free. Subscribe online at www.electronics-cooling.com. For subscription changes email info@electronics-cooling.com.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, or stored in a retrieval system of any nature, without the prior written permission of the publishers (except in accordance with the Copyright Designs and Patents Act 1988).

The opinions expressed in the articles, letters and other contributions included in this publication are those of the authors and the publication such articles, letters or other contributions does not necessarily imply that such opinions are those of the publisher. In addition, the publishers cannot accept any responsibility for any legal or other consequences which may arise directly or indirectly as a result of the use or adaptation of any of the material or information in this publication.

Electronics Cooling is a trademark of Mentor Graphics Corporation and its use is licensed to ITEM. ITEM is solely responsible for all content published, linked to, or otherwise presented in conjunction with the Electronics Cooling trademark.

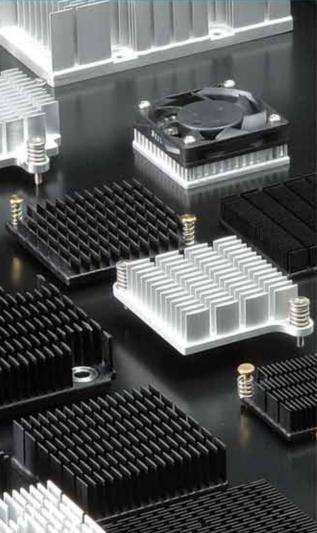

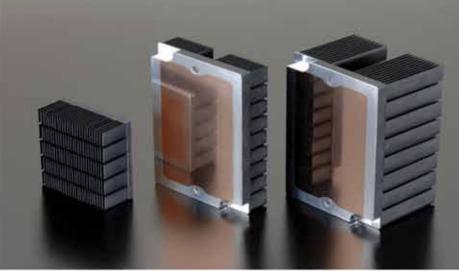

# Electronics cooling heat sink

Malico is not an "Ordinary" Company

We are a "Unique" and "Driven" family

Malico does not chase profits, instead we chase Zero Defects.

Quality is engineered into every part we make.

Our Customers count on Malico's reliability and advanced solutions capabilities.

Bring us your requirements and let us show you how we can both succeed!

### Malico Inc.

5,Ming Lung Road, Yangmei, 32663 Taiwan Tel:886-3-4728155 Fax:886-3-4725979 E-mail:inquiry@malico.com Website:www.malico.com

# **Cooling Matters**

# News in thermal management technologies

### CONTROLLING THERMAL CONDUCTIVITY TO IMPROVE ENERGY STORAGE

6/4/2014 - Researchers at the University of Illinois at Urbana-Champaign have experimentally shown for the first time that the thermal conductivity of lithium cobalt oxide (LixCoO2), a material used in the cathodes of lithium-ion batteries, can be reversibly electrochemically modulated over a significant range.

The new research on LixCoO2 represents "the first experimental demonstration of the electrochemical modulation of the thermal conductivity of a material, and, in fact, the only demonstration of large variable and reversible thermal conductivities in any material by any approach, other than very high pressure experiments."

During the experiment, researchers deposited a LixCoO2 film directly on a metal coated electrode, then immersed it in a common electrolyte. Time-domain thermoreflectance (TDTR) was used to measure the thermal conductivity of the lithium cobalt oxide thin film as a function of lithiation.

The study's findings are expected to significantly impact the field of electrochemical energy storage.

**Source: University of Illinois**

### SPIN WAVES TRANSPORT HEAT IN INSULATING MATERIALS

7/8/2014 - An international team of researchers has designed a nanoscale cooling element that utilizes fundamental subatomic properties to transport heat in electrical insulators.

The technology relies on the intrinsic spin of an electron that corresponds with its magnetic movement to move heat away from a component. While physicists have used spin for cooling purposes before, the The study, "Observation of the Spin Peltier Effect for Magnetic Insulators," new research marks the first time researchers have done so in insulating materials.

The latest study builds upon previous research demonstrating that directing an electric current through a magnetic layer causes the spins of the electrons in the current to all point in the same direction parallel to the magnetization.

This spin current can be used to influence the

temperature at the boundary between the surfaces of a nonmagnetic metal and a magnetic metal.

Source: Physical Review Letters

### SUPERCONDUCTING REFRIGERATOR COOLS VIA TUNNELING CASCADE

6/26/2014 - Researchers from Italy and France have proposed a new design for a superconducting refrigerator that uses a series of steps to more effectively cool objects down to temperatures near absolute zero.

The design for a multistage superconducting refrigerator, or "cascade cooler," from M. Camarasa-Gomez et al. adds an additional tunnel junction on each side (S2IS1INIS1IS2) of the SINIS design. In this case, when a voltage bias is applied to the S2, the hot quasiparticles tunnel from the normal metal to the S1 superconductors and then to the S2 superconductors, removing additional heat compared to the SINIS design. This multistage operation allows the refrigerator to easily cool a normal metal from a bath temperature of 0.5 K to 100 mK.

"[This is] a novel kind of electronic cooler based on hybrid superconducting tunnel junctions. A cascade geometry allows to cool a first superconducting stage, which is used as a local thermal bath in a second stage," they said.

The cascade cooling method could be easily implemented in a practical device, the researchers added, using a set of two additional junctions. The company hopes this cascading magnet technique could replace the traditional compressor and chemical refrigerant used in commercial refrigerators by the end of the decade.

**Source: Applied Physics Letters**

### **Datebook**

### **SEPTEMBER 9-11**

### **PCB West**

SANTA CLARA, CALIF., US http://pcbwest.com

### **SEPTEMBER 14-17**

### 42nd Annual Conference of NATAS

**SANTA FE, N.M., US**

www.natasinfo.org/ conferences/2014-42nd-annualconference

### **SEPTEMBER 16-18**

### The LED Show

LOS ANGELES, CALIF., US www.theledshow.com

### **SEPTEMBER 22-24**

### LEDS AND THE SSL ECOSYSTEM 2014

**CAMBRIDGE, MASS., US** www.ledsconference.com

OCTOBER 14-16 2014 www.emclive2014.com

A BRAND NEW, PRACTICAL, LIVE EVENT FEATURING WEBINARS, ROUNDTABLES, VIDEOS AND MORE

# ROUNDTABLE

### HEMP and IEMI Threats to Data Centers and Other Critical Facilities

This unique roundtable features vital information for data center managers who are concerned with current high-altitude electromagnetic pulse (HEMP) and intentional electromagnetic interference (IEMI) threats affecting the functionality of their servers. Moderator Bill Radasky will lead a discussion addressing the following questions:

- What are the characteristics and differences between the HEMP and IEMI threats?

- How do these electromagnetic transients relate to more commonly known EM transients such as ESD, lightning and radar?

- What parts of the critical infrastructures do you consider the most critical for HEMP and IEMI protection?

- How do you design protection from HEMP and IEMI to keep data centers safe?

- What is the role of existing lightning protection for protection from HEMP and IEMI?

- What is the role of standards in your approach to HEMP and IEMI hardening?

- What costs do you think are reasonable in protecting data centers from HEMP and/or IEMI?

REGISTER TODAY FOR THIS ROUNDTABLE DISCUSSION ON OCT. 15 AT 1:30PM

### **Virtual Prototyping**

**Peter Rodgers**

The Petroleum Institute

HE FOCUS of this article is on the use of computational fluid dynamics (CFD) as a virtual prototyping tool for electronics thermal design. However, first of all, given that this is my first thermal facts & fairy tales article, I decided to adopt the following quote as point of reference:

"In a utilitarian age, of all other times, it is a matter of grave importance that fairy tales should be respected." Charles Dickens (Frauds on the Fairies, 1853)

### **BACKGROUND**

Since the 1990s, CFD has been widely adopted in the electronics industry for the thermal design of electronic products and is progressively marching on to be considered by some to be a de facto virtual prototyping tool. Its advantages in terms of product improvements and enhanced productivity of design analysis are undisputed [1,2]. However, although not unsurprisingly reported, the industry has also found that incorrect product design decisions can be made as a result of inaccurate CFD predictions. The potential pitfalls of CFD analysis for electronics thermal design, in absence of supporting experimental characterization, are well documented [3,4]. To broaden the horizon of discussion on the capability of CFD analysis outside the field of electronics cooling, this article discusses the world of Formula One (F1) motorsport and NASA.

### **FORMULA ONE AERODYNAMICS**

Race pole position in F1 is often determined by hundredths of a second in qualifying. Consequently, car aerodynamics have become key to success, with budgets of tens of millions of dollars allocated for research and development each year [5]. To achieve optimum performance, the aerodynamic designer has two primary concerns: (i) the creation of downforce to promote car tire adhesion onto the track and improve cornering forces, and (ii) the reduction of drag generated by car body-induced turbulence.

To maximize aerodynamic performance, CFD is applied in parallel with wind tunnel characterization of scaled mock-up prototypes in wind tunnel environments to both develop and validate the design. However, an interesting departure to this strategy was adopted by one team for the 2010 and 2011 FIA F1 World Championships. Their car's aerodynamics design was undertaken primarily by simulation (i.e. CFD), bypassing experimentation on scaled prototypes. This CFD-only design approach has found previous success in American sports car racing, but at this point was unproven in F1, where aerodynamics are more complex. During the car's presentation at the start of the 2010 season [6], the team acknowledged that "there is scepticism about our approach," and said in relation to CFD, "We fully expect to encounter issues along the way. CFD (computational fluid dynamics) is an approximation, as is scale-model (wind-tunnel) testing. It is only when you hit the track that you can really appreciate the effect of factors that are tricky to model with any technology."

Although the car was found to lack aerodynamic performance throughout the 2010 season, with engine and driver factored for, the subsequent model that competed at the start of the 2011 F1 World Championship was again designed primarily by simulation [7], with some wind tunnel testing in late 2010 to try to resolve problems with the earlier design [8]. At the 2011 car's launch, the continued use of CFD as the primary design strategy was defended: "..those who don't believe in (the system) are members of the flat-earth society. It is the future of motor racing." [7]. However the car again faced performance difficulties, and by mid-season the team acknowledged, "What has been disappointing has been our pace. It's aero efficiency. We're nowhere with it." [8]. It was then also announced that the team would consider, budget permitting, a future wind tunnel testing programme. For the 2012 F1 World Championship, the car aerodynamics were actually developed through a combination of CFD and wind tunnel testing [9].

The CFD-driven design strategy, which was ultimately unsuccessful, had been motivated by the escalating, unsustainable costs of aerodynamics design in full-scale wind tunnels and on-track testing. This was recognized by the F1 team organization (FOTA) in 2009, with the introduction of a subsequent resource restriction agreement (RRA) to help constrain overall team expenditures. For example, in terms of aerodynamics, limitations were introduced on wind tunnel testing (in terms of wind-on time), as well as CFD processing (measured in

teraflops) due to the cost of high performance computing clusters, but with limited success [10]. Considerably greater restrictions were imposed in the 2014 FIA sporting regulations than in the previous RRA by the sport's governing body (FIA), with aerodynamic testing effectively reduced to nearly one-third of that allowed under the previous RRA [11]. Under the new FIA 2014 regulations, wind tunnel testing and CFD analysis are capped by a formula of 30 units (a unit being an hour per week of wind-on time, or a teraflop of compute capacity used for the solving of CFD cases) based on an eight-week aerodynamic testing period. For example, a team can use up to 30 hours per week of wind-on time, with no CFD processing, or 30 teraflop of CFD and no wind tunnel, or a combination of both. In addition, other restrictions were adopted on the number of wind tunnel runs (80) and operating time (60 hours) per week [11].

To help illustrate the implementation of the new regulations in the F1 aerodynamic design process, the following analogies were given by Sauber F1 team [12], between wind tunnel and hairdryer usage, and between CFD processing and computer usage: "You may be in the bathroom for 60 hours per week, but you may only switch on the hairdryer 80 times and not for longer than 30 hours in total. If your hairdryer runs 30 hours, you are not allowed to use your computer at all; less running time of your hairdryer will allow you to use your computer, but in any case you can't spend more time than 30 hours per week in total with your hairdryer and computer combined."

The introduction of the these restrictions is now leading to a greater emphasis on the use of CFD in F1 car aerodynamic development process, coupled with more efficient use of wind tunnel testing. However, not all F1 commentators agree that this is the best practice, given that the sport has often served as an innovator to the automotive industry. For example, concerns have arisen [13] that F1 may not be able to contribute to the rest of the CFD world in developing transient simulations, as future analysis maybe constrained to outdated teraflop-friendly steady-state science. Time will tell, but this story highlights the need for both optimization and effective use of CFD, combined with effective experimental characterizations. This strategy could be better implemented as part of an electronics cooling thermal design process.

### **NASA CFD VISION FOR 2030**

It might be tempting to believe that NASA's goals for CFD analysis do not apply to electronics cooling, however a recent report [14] commissioned by NASA presents altogether a series of seven findings, a vision for CFD capabili-

ties required by 2030, and a set of six recommendations for achieving these capabilities. All findings are equally applicable to electronics cooling, particularly Findings 3 and 4:

- Finding 3: The use of CFD in the aerospace design process is severely limited by the inability to accurately and reliably predict turbulent flows with significant regions of separation. Advances in Reynolds-averaged Navier-Stokes (RANS) modeling alone are unlikely to overcome this deficiency, while the use of Large-eddy simulation (LES) methods will remain impractical for various important applications for the foreseeable future, barring any radical advances in algorithmic technology.

- Finding 4: Mesh generation and adaptivity continue to be significant bottlenecks in the CFD workflow, and very little government investment has been targeted in these areas.

Among the six recommendations given to achieve the NASA 2030 vision of CFD capabilities, of particular interest to electronics cooling is the following:

Recommendation 4: NASA should lead efforts to develop and execute integrated experimental testing and computational validation campaigns.

### SUMMARY

Considering the experiences documented in other industries, such as the above, hopefully the fairy tale that the thermal design of electronics can somehow be achieved through virtual prototyping alone can be laid to rest for the foreseeable future.

### REFERENCES

[1] Tatchell, D., Parry, J., and Clark, I., "Advances in Cooling Electronics with CFD," NAFEMS World Congress, June 10-12, 2013, Salzburg, Austria.

[2] Seymour, M., Aldham, C., Warner, M., and Moezzi, H., "The Increasing Challenge of Data Center Design and Management: Is CFD a Must?" ElectronicsCooling, December 2011, http://www.electronics-cooling.com/2011/12/the-increasing-challenge-of-data-center-design-and-management-is-cfd-a-must/, last accessed July 31, 2014.

[3] Rodgers, P., and Eveloy, V., "CFD Prediction of Electronic Component Operational Temperature on PCBs," ElectronicsCooling, May 2004, http://www.electronics-cooling.com/2004/05/cfd-prediction-of-electronic-component-operational-temperature-on-pcbs/, last accessed July 31 2014.

[4] Lasance, C.J.M., "CFD Simulations in Electronic Systems: A Lot of Pitfalls and a Few Remedies," ElectronicsCooling, May 2005, http://www.electronics-cooling.com/2005/05/cfd-simulations-in-electronic-systems-a-lot-of-pitfalls-and-a-few-remedies/, last accessed July 31 2014.

[5] Formula1.com, "Aerodynamics,"

http://www.formula1.com/inside\_f1/understanding\_f1\_racing/5281.html, last accessed Inly 31, 2014

[6] BBC Sport, "Virgin 'Virtual' Formula 1 Challenger becomes Reality," February 3, 2010, http://news.bbc.co.uk/sport2/hi/motorsport/formula\_one/8495435.stm, last accessed July 31, 2014.

[7] Harris, R., "Russia back in F1 with Marussia Virgin Team," February 7, 2011, http://usatoday30.usatoday.com/sports/motor/2011-02-07-2658622712\_x.htm, last accessed July 31, 2014.

[8] The National, "Bahrain Grand Prix Awaits the Green Light," June 3, 2011, http://www.thenational.ae/sport/formula-one/bahrain-grand-prix-awaits-the-greenlight#ixzz3A6Aq6bCv, last accessed July 31, 2014.

[9] F1Technical, "Marussia MR01 Cosworth," March 5 2012, http://www.f1technical.net/forum/viewtopic.php?p=319175&f=12, last accessed July 31, 2014.

[10] Benson, A., Red Bull Set to dominate? December 6 2011, http://www.bbc.co.uk/blogs/legacy/andrewbenson/2011/12/red\_bull\_set\_to\_dominate.html, last accessed July 31, 2014. [11] Scarborough, C., "Analysis: Formula 1's New Aero Restrictions for 2014," December 13, 2013, http://www.autosport.com/news/report.php/id/111847, last accessed July 31, 2014. [12] Sauber F1 Team, "Absolute Beginner's Guide to 2014 Formula One" Regulations," http://www.sauberf1team.com/fileadmin/user\_upload/redactors/documents/pdf/2014\_Regulations\_EN.pdf, last accessed July 31, 2014.

[13] HPM, "CFD: Why Formula One is Creating Its Own (and Less Useful) Branch of the Science," January 28, 2013, https://www.highpowermedia.com/blog/3645/cfd-why-formula-one-is-creating-its-own-and-less-useful-branch-of-the-science, last accessed July 31, 2014.

[14] Slotnick J., Khodadoust, A., Alonso, J., Darmofal, D., Gropp, W., Lurie, E., and Mavriplis, D., "CFD Vision 2030 Study: A Path to Revolutionary Computational Aerosciences," NASA/CR-2014-218178, March 2014, http://ntrs.nasa.gov/search.jsp?R=20140003093, last accessed July 31, 2014.

The highest performing fans on the market.

Whether for cooling server rooms or switch cabinets, complex machines or sensitive medical technology - our intelligent and controllable high performance S-Force fans can be suited for many different applications. Each series represents the benchmark in its class with respect to air performance and pressure build-up with optimum motor efficiency and long service life. These compact fans reach nominal speeds up to 14,000 rpm and operating values that had previously been attained only by large fans or blowers. For more information: http://catalog.ebmpapst.us/sforce

The engineer's choice

### An Inexpensive Multi-channel AC Heater Control System

**Lucien François Dorthe and Paul Kolodner**

Bell Laboratories, Alcatel-Lucent, Inc.

### INTRODUCTION

COMMONLY-encountered problem in the experimental modeling of thermal-management solutions is the need to independently power many sources of heat. A typical telecomm circuit pack, for example, may contain a dozen or more integrated circuits (ICs) or optical components, and it is often desired to test cooling solutions by replacing each IC with an independently-computer-controlled resistive heater. This could be accomplished using multiple DC power supplies, but this approach is overly precise, bulky, and, worst of all, expensive—at least several hundred dollars per channel. This technical brief describes a much more economical system, using triac-based AC lamp dimmer modules originally intended for hobby or house-

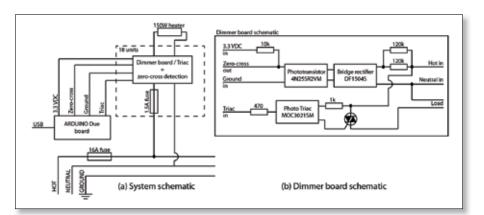

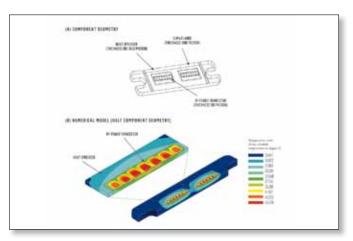

FIGURE 1: Multi-channel AC heater control system.

hold use. Controlled by an inexpensive processor board, this approach costs less than \$100 per channel.

ming AC lighting systems uses a triac

CIRCUIT DIAGRAM The standard circuit used for dim-

Lucien Dorthe obtained his master's degree in mechanical engineering at the Swiss Federal Institute of Technology of Lausanne in March 2014. His main fields of study are thermodynamics, energetics and heat transfer. He worked on several projects (modeling, simulation and experimental testing) to develop new methods like pump cycles or thermosyphons to cool electronic components using two-phase fluids.

Paul Kolodner recently retired from Bell Laboratories after a 34-year career. He was most recently a Distinguished Member of Technical Staff in the Thermal Management Group in the IP Routing Laboratory. He has performed experimental research on a variety of problems, including the use of rare-earthchelate films for high-resolution fluorescent thermal imaging, convective pattern formation, protein photobiology, precision microlens array characterization, applications of superhydrophobic surfaces, and thermal management of electronics. He has written or co-authored approximately 130 published papers and 40 issued or pending patents.

to control the connection of the load to the AC power source. The triac turns off the drive current after an adjustable time delay with respect to each zerocrossing of the AC waveform, and the user increases or decreases this delay to increase or reduce the time-averaged power. A small-format, single-channel dimmer module that performs this function is available for \$40 from a hobbyist website [1]. These circuits can switch 10 A, or 1.2 kW per channel at 120 Vac, and they can be modified for operation at higher currents. The system described herein uses 18 of these circuits, controlled by an Arduino Due processor module [2]. Arduino is an inexpensive, open-source electronics platform targeted towards hobbyists and educators (see [3] for complete information). Arduino processor modules contain a small microprocessor, programmable input/output pins, and USB ports, and they run code written in a simple, C-like language. The Arduino

Due module, which costs about \$50, is based on a 32-bit microcontroller running at a clock speed of 84 MHz. The module has 54 digital I/O pins, which would allow for control of up to 53 heater channels. The processor has 512 kB of flash memory for control code and is programmed by a computer running LabVIEW [4], via serial communication over the USB port.

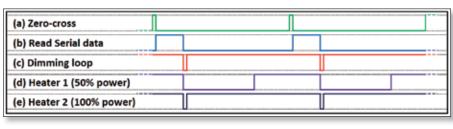

FIGURE 2: Timing diagram.

As shown in Figure 1(a), the Arduino

Due processor accepts a "zero-cross" input logic signal from one of the 18 dimmer modules (shown in Figure 1(b)); this signal consists of a train of short positive pulses that are synchronous with the sign changes of the AC waveform. Each of the 18 modules is assigned a separate "Triac" output pin on the Arduino board, and the program brings this signal high to connect that heater for the selected fraction of the AC waveform. The whole system is powered through the USB port.

The components are mounted inside a grounded aluminum electronics enclosure, which is mounted adjacent to the test fixture into which the 18 heaters have been clamped. This proximity allows the heater cables to be short and neat, reducing the risk of accidental disconnection. The heater cables are plugged into the control-circuit box using individual highcurrent, male electrical connectors to eliminate any shock hazard.

### **CODE AND TIMING ISSUES**

The control program is transferred to the Arduino board over the USB port. This program is included as an Appendix in the online version of this article and can also be requested by email from either of the authors. The code defines the input and output pins on the processor board and then runs several loops continuously, each of which is triggered once per half-

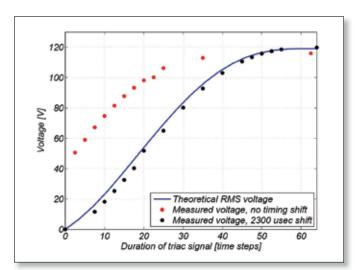

FIGURE 3: Measured and theoretical RMS output voltages as a function of the duration of the triac signal, for one heater channel.

cycle by the "zero-cross" signal. The "read loop" reads a string containing the 18 control parameters from the USB port. The "dimming loop" checks the on/off state of the 18 triacs and alters each at the time corresponding to the input parameter for that channel. A "delay loop" corrects the timing synchronization and allows the input string to be read, as detailed below.

Several timing and resolution issues affect the details of the code:

- 1. The zero-cross signal pulses precede the zero crossings by about 2.3 msec. Thus, the "delay loop" postpones the start of the "dimming loop" by this amount, relative to the zero-crossing pulses.

- 2. The serial input buffer of the Arduino processor is limited to 64 bytes. Therefore, the 18 power levels are encoded by a 56-byte string of 2-digit integers between 0 (full on) and 64 (full off), separated by commas and preceded by a start character ("s"). The time resolution step is 1/64th of a half-cycle, or 130 µsec, and the integers in the string represent the number of time steps in the "dimming loop" that elapse before each heater is turned on. At the fastest baud rate (112500 bit/sec), this string takes a bit less than 2.3 msec to read. This input is transferred once per halfcycle by the "read loop." The transfer takes place during the "delay loop."

- 3. The "dimming loop" checks the on/off state of each of the 18 triacs once every 130 usec and alters each according to the input string for that channel. Due to the limited speed of the Arduino Due processor, it was not possible to increase the timing resolution to 1/128th of a half-cycle in this implementation.

Figure 2 shows a diagram of the signal timing. The zerocross signal (trace (a)) triggers the "read loop" (trace (b)), which allows 2.3 msec for reading the serial data and synchronizes the start of the "dimming loop" with the actual zero-crossing of the AC waveform. Trace (c) shows the period available for the individual heaters to be turned on and off. Traces (d) and (e) show two representative triac signals.

### CONTROL CHARACTERISTICS

The control system was evaluated by measuring the AC output voltage of one channel with a true-RMS meter as the time delay was varied. A comparison between the measured

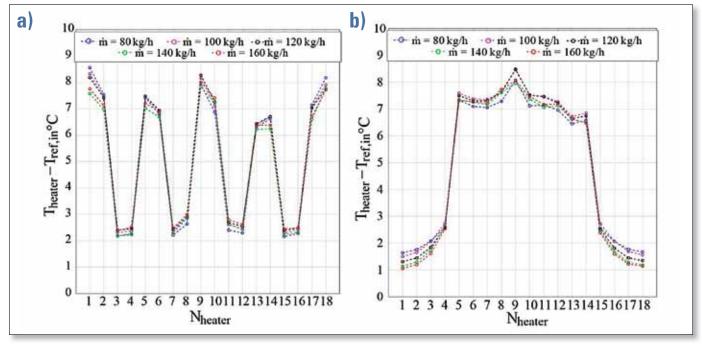

**FIGURE 4:** Measured spatial temperature profiles obtained with non-uniform heating using pumped refrigerant at different flow rates, m. a) Square-wave profile **b)** Rectangular profile

and theoretical RMS output voltages is presented in Figure 3. The blue curve shows the theoretical voltage, which is just the square root of the integral of a squared sine function. The red data points show the measured values with the length of the "delay loop" set to zero. The length of this delay was adjusted empirically to 2.3 msec in order to get the measured data points in black to overlap with the theoretical curve. The slight offset with respect to the theoretical curve indicates that this delay was set approximately 2 time steps too long.

### THERMAL PERFORMANCE

The heater control system was used to test a segmented aluminum cold plate cooled by pumped R134A refrigerant. The vertically-oriented cold surface has dimensions 417.5 mm wide x 80.0 mm high. Its interior consists of 18 vertical channels of height 53 mm, arrayed horizontally and connected in parallel to upper and lower manifolds, so that refrigerant flows upward through the channels. The test heaters each consist of a square copper bar of height 50 mm and width/depth 20 mm, with a vertical axial hole of diameter 6.35 mm holding a 140- $\Omega$  cartridge heater. Each bar also has an embedded thermocouple. The heaters were clamped against the cold surface, and the entire system is heavily insulated.

Figure 4 shows the thermal response of the system to non-uniform heating at five different refrigerant flow rates (ṁ) for two different spatial heating profiles. The plotted quantity is the heater temperature ( $T_{\text{heater}}$ ) relative to the input refrigerant temperature ( $T_{\text{ref,in}}$ ). All data used sub-cooling  $\Delta T_{\text{sub}} = 2\,^{\circ}\text{C}$  and total heating power 1,000 W. Figure 4(a) shows the result for a square-wave heating profile with period 4; low-power heaters

are off. In Figure 4(b), a rectangular profile was applied, with the center 10 heaters on and outer heaters off. The variations between the different curves suggest that (a) the power resolution in each channel is a few Watts, and (b) heater number 9 is running slightly hot, possibly because of a defect in its thermal interface. This performance has been more than adequate to allow the detailed characterization of this cold plate when operated as a gravity-driven thermosyphon.

### **CONCLUSIONS**

The control system described in this paper represents a new and useful compromise between cost, precision and flexibility. It is hard to imagine a cheaper way to control many heaters. The resolution and precision of this system is a few percent and could be improved if required. And, as to flexibility, the present implementation could be expanded to a channel count of 53 before a new architecture would be required. Because of the 64-bit word length of the Arduino Due module, a more complicated read protocol would be needed to increase resolution and/or channel count. Operating at higher powers could be enabled by replacing the triacs on the dimmer control modules.

### **REFERENCES**

- [1] iNMOJO, www.inmojo.com, last accessed July 31, 2014.

- [2] Arduino Due, http://arduino.cc/en/Main/arduinoBoardDue, last accessed July 31, 2014.

- [3] Arduino, http://arduino.cc/, last accessed July 31, 2014.

- [4] LabVIEW System Design Software, http://www.ni.com/labview/, last accessed July 31, 2014.

# INTRODUCING COOLSPAN® TECA

thermally & electrically conductive adhesive

### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

Visit us at PCB WEST September 10th Santa Clara, CA

Leading the way in...

• Support • Service • Knowledge • Reputation

### SCAN THE CODE TO GET OUR CONTACT INFO.

John Dobrick

Scott Kennedy Applications Development Eastern Territory (U.<u>S.)</u>

John Hendricks Regional Sales Manager

Kent Yeung

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

# **Estimating the Thermal Interaction between Vertically Stacked Chips in a Multi-Chip Package**

Je-Young Chang, Ashish Gupta Intel Corporation

### INTRODUCTION

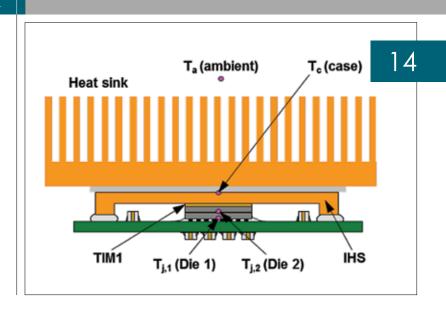

D INTEGRATION is considered a promising packaging technology option to increase transistor density by vertically integrating two or more dice with a dense high-speed interface with shorter interconnect length, enabling a smaller package form factor across a variety of market segments [1-2]. However, despite its promising electrical benefits, effective cooling of 3D stacked die packages remains a challenge [3-5], which could impact the long-term reliability of active devices in the package. In order to better understand and quantify the thermal response of 3D stacked die packages, accurate characterization of thermal behavior and establishment of appropriate thermal

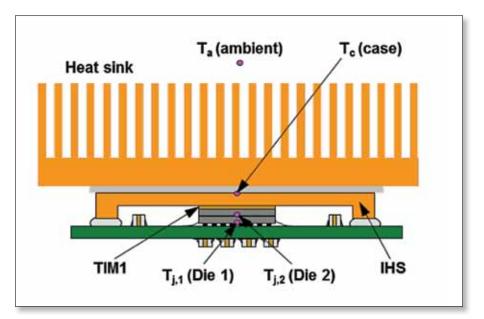

FIGURE 1: Schematic of speculative MCP with 3D die stack (Not drawn to scale).

**Je-Young Chang** received his B.S. and M.S. degrees from the Seoul National University in South Korea and his Ph.D. degree from University of Texas at Arlington, all in mechanical engineering. He worked at Penn State University for three years as a research associate before joining Intel in 2000. He has worked on many aspects of advanced cooling technologies, including two-phase immersion cooling, single/two-phase microchannel cooling, corrosion reliability of liquid cooling systems, heat pipes, TIMs, heat exchangers, etc. He has 19 issued/pending US patents, and more than 60 articles in archival journals, conference proceedings and Intel internal publications.

Ashish Gupta manages the Thermals/Fluids Core Competency Team in Intel's Assembly and Test Technology Development Group in Arizona. He holds a Ph.D. degree in Mechanical Engineering from Purdue University. His group is responsible for the R&D of advanced package thermal and cooling technologies, modeling methodologies and metrologies for Intel's current and future generations of processors for product segments during the discovery, definition, development and certification stages of technology maturity. The team's scope covers the entire gambit of Intel product segments across all market segments ranging from handheld devices and small form factor packages to higher power server products.

design rules for the feasibility of various integration options are essential.

In the previous article by the current authors [6], a thermal analysis methodology was presented for predicting cooling capabilities of Multi-Chip Package (MCP) architectures with multiple side-by-side dice. The thermal analysis methodology is based on the principle of linear superposition in conduction heat transfer to calculate the die junction temperatures at an arbitrary combination of powers applied to the dice under steady-state conditions [7-8]. In this article, the thermal analysis methodology is extended to predicting cooling capabilities of MCP architectures with 3D stacked dice.

# Welcome to Planet e.

The entire universe of electronics at a single location!

26th International Trade Fair for Electronic Components, Systems and Applications Messe München November 11–14, 2014 www.electronica.de

50 years electronica

# ESTIMATION OF COOLING ENVELOPE OF MC WITH 3D DIE STACK

In Figure 1, a typical 3D package architecture is illustrated with the locations of temperature measurements. As shown in the figure, the package has two dice stacked under an integrated heat spreader (IHS), which is cooled by a heat sink.

For the above 3D MCP in Figure 1, the same equation in the previous article [6] can be used to express the junction temperature of any of the dice as a function of the power(s) applied to all of the dice:

$$\begin{bmatrix} T_{j,1} \\ T_{j,2} \end{bmatrix} = \begin{bmatrix} \Psi_{11} & \Psi_{12} \\ \Psi_{21} & \Psi_{21} \end{bmatrix} \cdot \begin{bmatrix} P_1 \\ P_2 \end{bmatrix} = \Psi_{ca} \cdot (P_1 + P_2) + T_a \quad (1)$$

where  $T_{j,i}$  is the junction temperature of Die "i";  $P_i$  is the power dissipation of Die "i";  $\Psi$  matrix, also called the "influence" coefficient matrix, is the thermal resistance from the junction to the case;  $\Psi_{ca}$  (°C/W) is case-to-ambient thermal resistance; and  $T_{a}$  is the ambient temperature.

For the 3D MCP in Figure 1, the cooling envelope can be estimated using the same analysis methodology in the previous article [6]. For comparison purposes, a 2D planar MCP is also analyzed using the same power-maps and heat sink conditions. In 3D MCP, there is only one TIM1 interface (i.e., thermal interface material (TIM) between the die and IHS), over the die stack; however, additional thermal resistance at the die-to-die interface causes significant impact on the package cooling capability [3-5]. In the current analysis, considering the objective of this article, a thermally favorable die-to-die interface (i.e., a fully-populated thermal bump array at the die-to-die interface) is assumed for 3D MCP. Table 1 shows representative results from thermal simulations for two different cases of die power scenarios for each of the 3D and 2D MCPs.

For the above data of 3D MCP model, junction temperature differences from the reference point (e.g.,  $\Delta T_{_{j,i}} = T_{_{j,i}} - T_{_{c}}$ ) are considered in actual calculations, while the downstream variables (i.e.,  $\Psi_{_{ca}}$  and  $T_{_{a}}$ ) are assumed constant. In this case, all the calculation results (i.e.,  $\Delta T_{_{j,i}}$  and  $P_{_{i}}$  values) can be summarized as:

$\begin{bmatrix} 11.78 \\ 6.52 \end{bmatrix} = \begin{bmatrix} \Psi_{11} & \Psi_{12} \\ \Psi_{21} & \Psi_{22} \end{bmatrix} \cdot \begin{bmatrix} 60 \\ 20 \end{bmatrix} \text{ and } \begin{bmatrix} 17.67 \\ 9.34 \end{bmatrix} = \begin{bmatrix} \Psi_{11} & \Psi_{12} \\ \Psi_{21} & \Psi_{22} \end{bmatrix} \cdot \begin{bmatrix} 95 \\ 10 \end{bmatrix}$ (2)

Equation (2) can be rearranged for each of  $\Delta T_{j,1}$  and  $\Delta T_{j,2}$  values, and "power input" matrix can be expressed as:

$$\begin{bmatrix} 11.78 \\ 17.67 \end{bmatrix} = \begin{bmatrix} 60 & 20 \\ 95 & 10 \end{bmatrix} \cdot \begin{bmatrix} \Psi_{11} \\ \Psi_{12} \end{bmatrix} \text{ and } \begin{bmatrix} 6.52 \\ 9.34 \end{bmatrix} = \begin{bmatrix} 60 & 20 \\ 95 & 10 \end{bmatrix} \cdot \begin{bmatrix} \Psi_{21} \\ \Psi_{22} \end{bmatrix}$$

(3)

For Equations (1) to (3), the values of  $\Psi$  matrix elements can be calculated from an inverse matrix solver, and the complete form of Equation (1) for the 3D MCP in Table 1 can be written as:

$$\begin{bmatrix} T_{j,1} \\ T_{i,2} \end{bmatrix} = \begin{bmatrix} 0.181 & -0.045 \\ -0.094 & 0.045 \end{bmatrix} \cdot \begin{bmatrix} P_1 \\ P_2 \end{bmatrix} + \Psi_{ca} (P_1 + P_2) + T_a$$

(4)

Using the same procedure, the complete form of Equation (1) for the 2D MCP in Table 1 can be derived as:

$$\begin{bmatrix} T_{j,1} \\ T_{i,2} \end{bmatrix} = \begin{bmatrix} 0.116 & -0.083 \\ -0.060 & 0.213 \end{bmatrix} \cdot \begin{bmatrix} P_1 \\ P_2 \end{bmatrix} + \Psi_{ca} (P_1 + P_2) + T_a$$

(5)

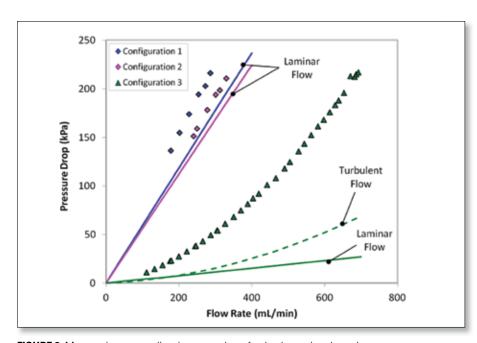

## GRAPHICAL REPRESENTATION OF MCP COOLING ENVELOPES

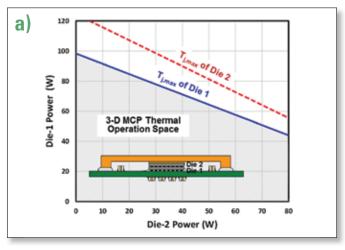

For both Equations (4) and (5), there are two linear equations expressed in terms of  $P_1$  and  $P_2$ , which represent cooling capabilities of Die 1 and Die 2 as defined by junction temperature limits and ambient temperature condition [6]. In Figures 2(a) and 2(b), cooling capabilities of 3D and 2D MCPs, respectively, in Table 1 are illustrated. In each figure, the solid lines represent the cooling capabilities of Die 1 and Die 2 with respect to junction temperature limits and ambient temperature condition, and the overlapped region (highlighted with gray color) represents thermal operation space of the MCP.

As shown in Figure 2(a), 3D MCP shows a strong thermal

coupling between two dice due to close proximity in 3D stacked configuration, as indicated by the similarity in the slopes of the two junction temperature limiter lines. This can be clearly compared with the analysis results of 2D MCP in Figure 2(b), where the junction temperature limiter lines have very dissimilar slopes. In the extreme case, if there is no thermal cross talk between two dice, the junction temperature limiter lines should be perpendicular each other.

| TABLE 1: EXAMPLE TEMPERATURE DATA FOR MCP ANALYSES  |  |

|-----------------------------------------------------|--|

| $(\Psi_{CA} = 0.24  ^{\circ}\text{C/W IS ASSUMED})$ |  |

| $(\Psi_{CA} = 0.24  ^{\circ}\text{C/W IS ASSUMED})$ |              |        |              |        |  |

|-----------------------------------------------------|--------------|--------|--------------|--------|--|

|                                                     | 3D MCP Model |        | 2D MCP Model |        |  |

|                                                     | Case 1       | Case 2 | Case 3       | Case 4 |  |

| Die-1 power [W]                                     | 60           | 95     | 60           | 95     |  |

| Die-2 power [W]                                     | 20           | 10     | 20           | 10     |  |

| $\Delta T_{j,1} = T_{j,1} - T_{c} [\circ C]$        | 11.78        | 17.67  | 5.29         | 10.17  |  |

| $\Delta T_{j,1} = T_{j,2} - T_c [^{\circ}C]$        | 6.52         | 9.34   | 0.67         | -3.55  |  |

**FIGURE 2:** Cooling envelopes of speculative MCPs at steady-state conditions ( $T_{i,max} = 95$  °C for both dice,  $T_a = 54$  °C, and  $\Psi_{ca} = 0.24$  °C/W are assumed). a) 3D MCP, b) 2D planar MCP.

As shown in Figure 2(a), for a 3D MCP, junction temperature limiter of either die can determine the whole thermal operation space, thus if it is set at too low a value (e.g., 80 °C for memory die), the package cooling capability can be significantly impacted. In the current analyses, both dice are assumed to have the same junction temperature limit (95 °C). For a speculative 3D MCP in Figure 1, the bottom and top dice could be logic and memory chips, respectively. In this case, it is imperative that  $T_{_{\mathrm{i},\mathrm{max}}}$  of memory die should be kept as close possible to  $T_{i,max}$  of logic die to ensure thermal management of 3D package under control, as long as memory performance (e.g., memory refresh rate, leakage) and reliability requirements can be met.

The above graphical representations of the cooling envelopes of both 2D and 3D MCPs are useful to estimate thermal operation spaces for different design conditions, such as different junction temperature limits, ambient temperatures and heat sink designs. It should be noted that, for accurate estimation of thermal operation space, the Ψ matrix should be re-calculated, if there is any significant change in:

- a. Design conditions, such as die dimensions, die locations, die-to-die spacing, die-to-die interface in 3D die stack, IHS dimensions, etc.

- **b.** Material conductivities, such as thermal interface conductivity.

- c. Die non-uniform heating power-maps.

Finally, as more and more dice are integrated into 3D packages, there will be more frequent examples of a combination of "side-by-side" and "vertically stacked" dices. Both analysis results of the previous [6] and current articles have demonstrated that the principle of linear superposition is applicable to any configuration of multiple dice in an MCP with conduction being the dominant heat transfer mechanism, and provide the first order approximation of the system.

### **REFERENCES**

- [1] B. Black, et al., "Die Stacking (3D) Microarchitecture," 39th International Symposium on Microarchitecture, pp. 469-479, 2006.

- [2] J.U. Knickerbocker, et al., "Three Dimensional Silicon Integration," IBM Journal of Res. & Dev., Vol. 52, No. 6, pp. 553-567, 2008.

- [3] K. Matsumoto, et al., "Experimental Thermal Resistance Evaluation of a Three-Dimensional (3D) Chip Stack," 27th IEEE SEMI-THERM Symposium, pp. 125-131, 2011.

- [4] E. Colgan, et al., "Measurement of Microbump Thermal Resistance in 3D Chip Stacks," 28th IEEE SEMI-THERM Symposium, pp. 1-7, 2012. [5] H. Oprins, et al., "Steady State and Transient Thermal Analysis of Hot Spots in 3D Stacked ICs using Dedicated Test Chips," 27th IEEE SEMI-THERM Symposium, pp. 116-125, 2011.

- [6] J.-Y. Chang, and A. Gupta, "Estimating the Thermal Interaction between Multiple Side by Side Chips on a Multi-Chip Package," ElectronicsCooling, pp. 14-17, June 2014.

- [7] B. Guenin, "So many Chips, So Little Time; Device Temperature Prediction in Multi-Chip Packages," ElectronicsCooling, Vol. 12, No. 3, August 2006.

- [8] R. Stout, "Part One: Linear Superposition Speeds Thermal Modeling," Power Electronics Technology, pp. 20-25, January 2007.

# High Heat Flux, Single-Phase Microchannel and Minichannel Cooling with Water and Liquid Metal

Rui Zhang<sup>1</sup>, Marc Hodes<sup>1</sup>, Nathan Lower<sup>2</sup> and Ross Wilcoxon<sup>2</sup> Rockwell Collins<sup>2</sup>. Tufts University<sup>1</sup>

**Rui Zhang** received her B.S. from Shandong University in China in 2009, where she majored in energy and power engineering with an emphasis on the design and operation of heat exchangers and boilers in power plants. In 2011, she received her M.S. in mechanical engineering from Tufts University, Medford, Mass., where her research focused on optimization of thermoelectric module-heat sink assemblies for minimal power consumption for precision temperature control of photonic components. She recently completed her Ph.D. degree in the mechanical engineering department at Tufts University on water-based microchannel and Galinstan-based minichannel cooling beyond 1 kW/cm² heat fluxes.

Marc Hodes received his MS in mechanical engineering from the University of Minnesota, where he researched microelectronics dielectric liquid cooling, and a Ph.D. in mechanical engineering from the Massachusetts Institute of Technology, where he researched salt deposition (fouling) in supercritical water oxidation reactors. After more than 10 years at Bell Labs, he joined the Tufts University Mechanical Engineering Department in 2008 as an associate professor. His research areas include aerogel thermal insulators; heat transfer in microchannels containing superhydrophobic nanostructured surfaces; increasing the conversion efficiency of thermoelectric modules for precision temperature control and power generation; and liquid metal heat sink optimization.

Nathan Lower received his B.A. in mathematics, physics, and computer science from Coe College in 2001. After completing his Ph.D. in Ceramic Engineering at the University of Missouri-Rolla in 2004, he joined the Rockwell Collins Advanced Technology Center and is currently a principal mechanical engineer. He specialized in microelectronic system development, miniaturization, material development, thermal management, 3D MEMS fabrication and processing, and electroplating and PCB fabrication. During this time, he has developed a number of novel packaging and thermal management technologies, including Z-Fab (3D microfabrication process), electroformed die attach, inorganic thermal and protective composite materials and liquid metal cooling techniques.

Ross Wilcoxon received B.S. and M.S. degrees in mechanical engineering from South Dakota State University and a Ph.D. in mechanical engineering from the University of Minnesota. Prior to joining Rockwell Collins in 1998, he was an assistant professor at South Dakota State University. He is a principal mechanical engineer in the Rockwell Collins Advanced Technology Center where he conducts research and supports product development related to component reliability, electronics packaging and thermal management. He currently holds 23 U.S. patents.

### INTRODUCTION

ICROCHANNEL HEAT sinks provide significant opportunities for enhanced thermal management technology through

a combination of increased surface area and small length scales that lead to very low thermal resistance. In addition to providing surface area enhancement, microchannel cooling exploits the fact that the convective heat transfer coefficient in fully-developed laminar flow is inversely proportional to the hydraulic diameter. Therefore, although the caloric resistance of microchannels,  $1/(\dot{m}c_p)$ —where  $\dot{m}$  is mass flow rate and  $c_p$  is specific heat—is high, extreme heat fluxes may be accommodated.

Tuckerman and Pease [1] introduced the thermal community to the opportunities afforded by microchannel cooling in 1981. They achieved a thermal resistance of 0.09 °C/W when a heat flux of 790 W/cm² was imposed on a 1 cm  $\times$  1 cm footprint portion of a 400  $\mu m$ -thick silicon substrate utilizing single-phase water as the coolant. Their result remains the benchmark today.

In this study, the cooling potential of alternate fin configurations in microchannel heat sinks with both water and liquid metal as the coolant is investigated, based on the same physical constraints (1 cm  $\times$  1 cm  $\times$  400  $\mu$ m heat sink volume, and total pressure drop of 214 kPa) as reported in Tuckerman and Pease [1]. Testing showed that under these constraints an optimized water-cooled microchannel test section

achieved a heat flux of 1002 W/cm<sup>2</sup> with thermal resistance of 0.071°C/W. For a liquid metal-cooled heat sink with larger minichannels, testing was constrained by high pressure drops in the test section that that limited the coolant flow rate. However, this configuration did demonstrate a minimum thermal resistance of 0.077°C/W under similar temperature and pressure drop constraints as used in [1] and, with a higher temperature limit, achieved a maximum heat flux of 1.5 kW/cm<sup>2</sup>.

### **BACKGROUND**

Hodes et al. [2] reviewed the literature on subsequent investigations and developed a first-order model that predicted that thermal resistance can be reduced by 23% and 40% using optimal waterbased microchannel and Galinstan -based minichannel heat sinks, respectively, under the constraints imposed by Tuckerman and Pease [1].

Galinstan<sup>2</sup> is a liquid at room temperature and its thermal conductivity of 16.5 W/m.K (i.e. 28 times that of water) results in high convection heat transfer coefficients. Wilcoxon et al. [3] demonstrated its use as a coolant in a threelayer FR-4 prototype that included an integrated magnetohydrodynamic pump

and achieved an effective thermal conductivity of 6,000 W/m.K. Due to the density and viscosity of Galinstan being ~6 and ~2.4 times that of water [3], respectively, it exhibits a relatively high flow resistance. In addition, Galinstan has a volumetric heat capacity ( $\rho c_n$ ) that is approximately one-half that of water [4], which further increases the caloric thermal resistance. Therefore, the flow resistance must be reduced when the coolant is changed from water to Galinstan and optimal channel spacing will vary significantly depending on the coolant [2]. For the geometry constraints of this study, the majority of the total thermal resistance for water is due to the convective thermal resistance (1/(hA)); however, with Galinstan the caloric thermal resistance  $(1/(\dot{m}c_n))$ is much more significant. Therefore, for a prescribed pressure drop, Galinstan requires larger flow channels (i.e., minichannels) that enable sufficiently high flow rates to minimize caloric thermal resistance.

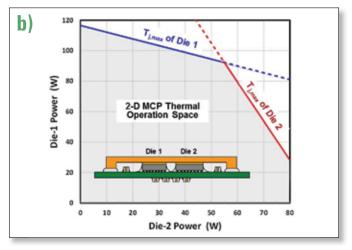

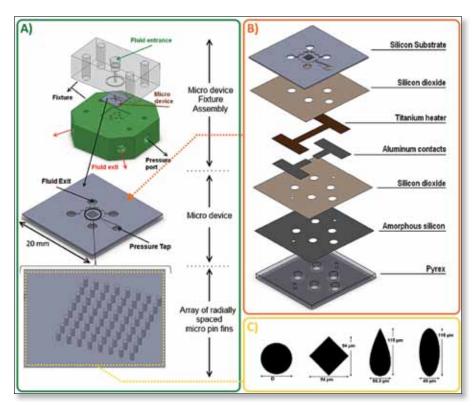

FIGURE 1: Exploded view of microchannel test section.

| TABLE 1: MICROCHANNEL TEST SECTION GEOMETRIES |                                                               |     |                         |     |    |

|-----------------------------------------------|---------------------------------------------------------------|-----|-------------------------|-----|----|

| Configuration                                 | Channel Wall Coolant Width [µm] Wall Thickness [µm]  Channels |     | Heater<br>Size<br>[mm²] |     |    |

| 1                                             | Water                                                         | 50  | 50                      | 100 | 98 |

| 2                                             | Water                                                         | 44  | 20                      | 160 | 90 |

| 3                                             | Galinstan                                                     | 334 | 26                      | 28  | 92 |

### **TEST SECTION AND EXPERIMENTAL APPROACH**

Three different heat sink geometries, specified in Table 1, were tested in this study. The heat sinks consisted of a 400 μm-thick float-zone silicon substrate into which 302 μm-tall channels were cut to a controlled depth using a Disco (Model DAD321) dicing saw. A titanium-tungsten (TiW) heating element, slightly less than 1 cm<sup>2</sup> in size to account for any misalignment with the fins, was sputtered onto the other side of the substrate. Configuration 1 was similar to that utilized by Tuckerman and Pease [1], Configuration 2 was optimized using the methodology of [2] and Configuration 3 had a minichannel geometry optimized for use with Galinstan. Figure 1 shows an exploded view of the test section. Details on the test section fabrication and assembly processes are described in [4].

### **TEST SETUP**

Coolant was pumped through the test sections with a magnetically driven gear pump. Liquid passed through a heat exchanger that was cooled with an external liquid chiller to maintain a test section inlet temperature of 20°C. Temperatures were monitored using Type-T thermocouples at the test section inlet and outlet and the pressure difference across the test section was measured using an Omega® PX409 differen-

<sup>&</sup>lt;sup>1</sup> The thermal resistance is defined as  $R = (T_{max} - T_{in})/q$ , where q is the heat dissipation,  $T_{max}$  is the highest measured temperature on the heating element and  $T_{in}$  is the inlet temperature of the liquid.

<sup>&</sup>lt;sup>2</sup> Galinstan is the trade name of a eutectic alloy of gallium, indium and tin developed by Geratherm Medical AG (Geschwenda, Germany) and is used as a non-toxic replacement for mercury in oral thermometry.

tial pressure transducer. An infrared (IR) camera was used to measure the temperatures of the heater, which had been painted.

Water testing used an open loop in which a steady flow of deionized (DI) water was supplied to an open beaker from which the pump drew out a controlled rate. The water was then pumped through a 5 µm filter. Galinstan testing was conducted with a closed loop that recirculated the liquid metal and included a custom stainless steel filter designed to remove any oxidized particles of the Galinstan that could block test section channels. The filter included a mesh screen and also was oriented with the exit below the entrance so that lower density particles would separate from the flow.

### **EXPERIMENTAL TEST RESULTS**

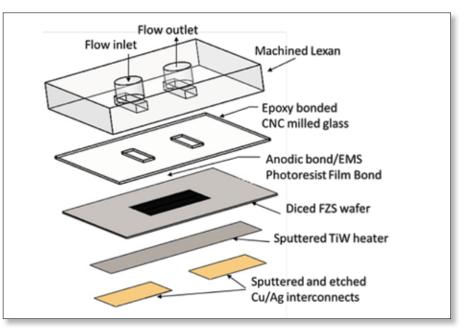

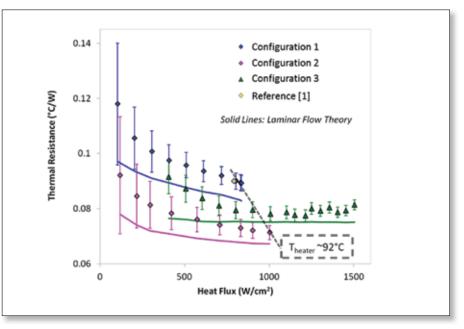

Figure 2 shows the measured thermal resistance as a function of heat flux for the three configurations. In each test, the total system pressure drop was held constant at  $212 \pm 2$  kPa. Testing with water was limited to the maximum average heater temperature of ~92 °C indicated in the figure. The thermal resistance values shown in this figure are based on the average temperature of the trailing edge of the heater and are normalized to a heater area of 1 cm². Configuration 1 testing reproduced the thermal resistance, and exceeded the maximum heat flux, reported in [1] while the results for

**FIGURE 3:** Measured versus predicted pressure drops for the three microchannel test section configurations defined in Table 1.

**FIGURE 2:** Measured versus predicted thermal resistances for the three microchannel test section configurations defined in Table 1.

Configuration 2 demonstrated that the optimized microchannel geometry achieved a minimum thermal resistance of 0.071°C/W, which is ~21% lower than reported in [1] with a maximum heat flux of over 1kW/cm². The thermal resistance of the Galinstan minichannels (Configuration 3) fell between those of the other two configurations. Because Galinstan has a boiling point >1,300 °C, Configuration 3 could operate at higher heat fluxes to a maximum value of more than 1.5 kW/cm². At this heat flux, the average heater temperature was 157

°C with a peak hot spot temperature of 174 °C. Error bars in the plot indicate the measurement uncertainty as calculated using the method presented by Kline and McClintock [5]. Solid lines in the plot indicate the thermal resistance values predicted for laminar flow through the heat sinks.

Symbols in Figure 3 show the experimentally measured overall pressure drop in the test section as a function of coolant flow rate. The lines indicate the predicted pressure drop associated with flow through the channels (flow through the channels as well as channel entrance/exit effects) for each configuration; both laminar and turbulent predictions are shown for the configuration for liquid metal cooling.

### **DISCUSSION**

Thermal resistance results for the water-cooled microchannel heat sinks re-

produced thermal resistance reported by Tuckerman and Pease [1] and demonstrated the efficacy of the more comprehensive optimization method proposed by Hodes et al. [2] that reduced the thermal resistance by 21%. Measured thermal resistances were generally ~10% higher than laminar flow theory predictions. This relatively small offset is likely due to a combination of non-uniformities in the flow distribution, imperfections in the fin geometry and some contribution of conduction through the silicon substrate between the heater and the fins. The liquid metal minichannel heat sink did demonstrate a low thermal resistance of 0.077°C/W and the ability to cool heat fluxes up to 1.5 kW/cm<sup>2</sup>. However, it did not achieve the extremely low thermal resistance performance predicted by Hodes et al. [2], primarily due to the fact that flow rate was limited to less than 700 mL/min. This limitation can be best understood by comparing the measured system pressure drop and predicted channel drops of the three configurations, shown in Figure 3.

Due to the extremely small hydraulic diameter of the microchannels, the system pressure drops in Configurations 1 and 2 are dominated by the channel pressure drop. In contrast, the minichannels in Configuration 3 have a much smaller contribution to the overall pressure drop, even if the flow is turbulent. In the liquid metal heat sink, the 'minor' losses associated with the complex three-dimensional flows entering and leaving the test section actually led to the majority of the overall pressure drop. Improved design of the flow in the test section would greatly reduce these pressure drops and allow the flow rate to increase. The optimized geometry of Configuration 3 was based on predictions with a flow rate of ~1,300 mL/min rather than the ~700 mL/min that was achieved with the current test setup.

### CONCLUSIONS

Microchannel heat sinks that utilize single-phase water as the coolant at high heat fluxes were tested and experimental data, which agreed well with theoretical predictions, for the flow and thermal resistance were provided for two different configurations. The authors validated the results reported by Tuckerman and Pease [1] for a thermal resistance of 0.09°C/W and demonstrated an optimized geometry based that cooled a heat flux of 1002 W/cm<sup>2</sup>, with a lowest reported thermal resistance of 0.071°C/W. Galinstan-based heat sinks demonstrated a thermal resistance as low as 0.077°C/W, which could be further reduced with an increased flow rate. Configuration 3 (with liquid metal) had higher than expected inlet/outlet pressure drops that prevented operating the liquid metal cooled minichannel heat sinks at their full potential. Testing with liquid metal did demonstrate an exceptionally high heat flux capacity of more than 1.5 kW from an area of ~1cm<sup>2</sup>.

### **ACKNOWLEDGMENTS**

This work was supported by DARPA Grant No. W31P4Q-11-1-0011. The authors would like to acknowledge

the contributions of David Westergren, Dave Dlouhy, Doug Twedt, Jennifer McAllister and Andy Walker of Rockwell Collins.

### **REFERENCES**

[1] D. Tuckerman and R. Pease, "High-Performance Heat Sinking for VLSI," IEEE Electron Device Letters, Vol. EDL-2, No. 5, pp. 126-129, 1981.

[2] M. Hodes, R. Zhang, L. S. Lam, R. Wilcoxon, and N. Lower, "On the Potential of Galinstan-Based Minichannel and Minigap Cooling," IEEE Transactions on Components, Packaging and Manufacturing Technology, Vol. 4, No. 1, pp. 46-56, 2014. [3] R. Wilcoxon, N. Lower, and D. Dlouhy, "A Compliant Thermal Spreader with Internal Liquid Metal Cooling Channels," 26th Annual IEEE Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM 26), pp. 210-216, March, 2010.

[4] R. Zhang, M. Hodes, N. Lower, and R. Wilcoxon, "Water-Based Microchannel and Galinstan-Based Minichannel Cooling beyond 1kW/cm2 Heat Fluxes", submitted to IEEE Transactions on Components, Packaging and Manufacturing Technology, 2014.

[5] S. J. Kline, and F. A. McClintock. "Describing Uncertainties in Single-Sample Experiments", Mechanical Engineering, Vol. 75, No. 1 pp. 3-8, 1953.

### **CVD Diamond – Integrating a Superior Thermal Material**

Thomas Obeloer, Bruce Bolliger

Element Six

### INTRODUCTION:

S SEMICONDUCTOR devices continue to increase in power density, heat fluxes are becoming extremely high (several tens of kW/ cm<sup>2</sup>), and can represent, for example in GaN RF devices, five times that of the sun's surface. This trend is increasing thermal management challenges for these electronic devices. It has been as stated by various sources [1] that heat related issues are a common cause of failures in high-end electronic systems. This can be for both a catastrophic failure due to devices exceeding allowable operating temperatures as well as failure to achieve required system lifetime due to exposure to elevated thermal loads and possibly leading to failures in interfaces, connections or the device itself.

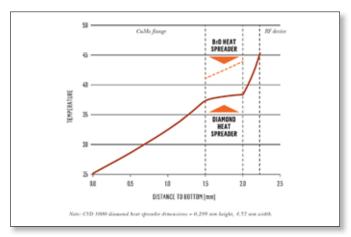

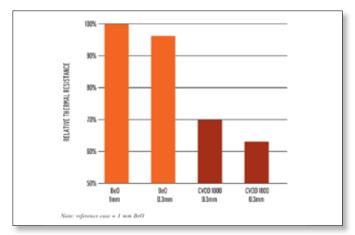

This article covers several important issues that advanced thermal solutions,

particularly for RF power amplifiers, must address. Here, we are concentrating on new materials, such as CVD (chemical vapour deposition) diamond as a heat spreader to reduce overall package thermal resistance compared to today's more commonly used materials for thermal management. A practical application example of an RF device mounted on a CVD diamond heat spreader is modeled and analyzed for its impact on the overall package thermal resistance.

### **CVD DIAMOND**

Diamond possesses a remarkable set of properties including the highest known thermal conductivity, stiffness and hardness, combined with high optical transmission across a wide wavelength range, low expansion coefficient and low density. These characteristics can make diamond a material of choice for thermal management

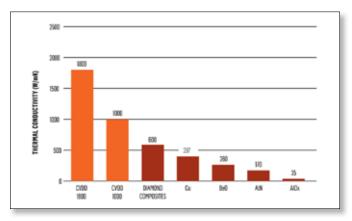

to significantly reduce thermal resistance. To synthesize the diamond for this purpose, the first step is choosing the most suitable deposition technology. Microwave-assisted CVD enables the best control of grain size and grain interfaces to generate highquality, high repeatability, polycrystalline diamond at the thermal conductivity level needed for particular applications. CVD diamond is now readily commercially available in different grades with 1,000-2,000 W/m-K thermal conductivities. Also very important is the fact that CVD diamond has fully isotropic characteristics, enabling enhanced heat spreading in all directions. Figure 1 shows a comparison of the thermal conductivity of CVD diamond with other materials traditionally used for heat spreading purposes.

With recent technology advances, CVD diamond has become readily available in volume and costs have declined rapidly. Unmetallized CVD diamond heat spreaders are available today at a typical volume cost of \$1/mm3. Prices vary dependant on the thermal-conductivity grade used. With a typical thickness between 0.25 - 0.40 mm and lateral dimensions equal to the die size, a diamond heat spreader for RF devices will often be less than 5 mm<sup>3</sup> in size. Thus, for an incremental cost of a few dollars at the chip level, system costs can be substantially reduced. For instance, enabling system operation at an elevated temperature can reduce both the initial cost of the cooling sub-system and the on-going operating cost as well. And using an appropriate die-attach method, diamond heat spreaders provide reliable thermal management solutions for semiconductor packages [2].

**Thomas Obeloer** is the business development manager at Element Six based in Santa Clara, California. Obeloer holds a Master's Degree in mechanical engineering and has more than 20 years of experience in the area of advanced thermal management, primarily in the field of advanced materials such as CVD diamond.

**Bruce Bolliger** is the head of semiconductor business at Element Six, where he leads worldwide semiconductor industry business development for synthetic diamond applications. He brings more than 20 years of experience in manufacturing, business development and marketing to his current role, as well as seven years of operations management experience in Asia. Prior to joining Element Six, Bolliger served as head of service solutions organization for test and measurement device manufacturer, Tektronix, in Singapore. In this role, he was responsible for aftersales support of product lines across the Asian market, and is credited with started new calibration service business in China, India and Japan.

Thermal Innovations for a Cool World

Semiconductor Thermal Measurement, Modeling and Management Symposium

T. H. I. R. T. Y. - F. I. R. S. T. A. N. N. U. A. I.

### CALL FOR PAPERS

March 15-19, 2015

DoubleTree Hotel, San Jose, CA, USA

### The conference

SEMI-THERM is an international forum dedicated to the thermal management and characterization of electronic components and systems. It provides knowledge covering all thermal length scales from IC to facility level. The symposium fosters the exchange of knowledge between thermal engineers, professionals and leading experts from industry as well as the exchange of information on the latest academic and industrial advances in electronics thermal management. Areas of interest include, but are not limited, to the following:

### Topics:

- Component, Board- and System-Level Thermal Design Approaches

- Air mover technologies with low acoustics

- Thermal Integration in the Product Design Process

- Multi-Physics Based Reliability, including Accelerated Testing

- Multi-objective design and optimization, modeling and characterization

- Novel materials: Heat Spreaders, Thermal Vias and Thermal Interface Materials

- Nanotechnology: Thermal, Mechanics, Material and Process Related Issues in Nanostructures

- Micro-Fluidics

- Characterization and Standardization of Material Property Measurements

- Energy Harvesting materials, Thermo-electrics

- Novel and Advanced Cooling Techniques/Technology,

- Roadmaps, Specifications and Traditional Cooling Limits

- Mechanical Modeling, Simulations and Characterization

- Characterization and Modeling of Multi-Scale Heat Transfer Problems

- Computational Fluid Dynamics (CFD) Analysis and Validation

- Multi-physics Modeling and Characterization of Products and Processes

- Thermal Control Methodologies

### **Application areas:**

- Processors, ICs, and Memory

- 3-D electronics

- Wireless, Network, Computing Systems

- Data Centers

- Portable and Consumer Electronics

- Power Electronics

- Harsh Environments

- Commercial, Defense, and Aerospace Systems

- Solid-State Lighting

- Solid State Energy Generation/Cooling

- Medical and Biomedical electronics

- Instrumentation and Controls

- Micro- and nano-scale devices

- MEMS and sensors

- Alternative and Renewable Energy

- Wearables

### **Conference highlights**

- Dedicated sessions on various application areas, novel materials, thermo-mechanical modeling/characterization techniques

- Two days of short courses (March 15 and 16, 2015), embedded tutorials and technical workshops

- Vendor exhibits: Cooling technologies, Air movers, Experimental characterization equipment and CFD simulation software

### To submit an abstract

You are invited to submit an extended abstract describing the scope, contents, key results, findings and conclusions. This abstract of 2 to 5 pages is supported by figures, tables and references as appropriate. **Abstracts must demonstrate high technical quality, originality, potential impacts. Upload your abstract electronically** in RTF, DOC or PDF formats at www.semi-therm.org

| Abstract Submission Deadline | sion Deadline Abstract Acceptance Notification Photo-ready Full Manu |                 |

|------------------------------|----------------------------------------------------------------------|-----------------|

| September 29, 2014           | November 3, 2014                                                     | January 5, 2015 |

SEMI-THERM actively solicits student papers, students to co-chair sessions, and awards travel stipends and reduced conference fees.

For further information please contact the Program Chair:

Rahima Mohammed, Principal Engineer, Intel Corporation, E-mail: rahima.k.mohammed@intel.com

Visit our website: http://www.semi-therm.org

FIGURE 1: Comparison of thermal conductivity of CVD diamond and other, 'traditional' heat spreading materials [2, 3]

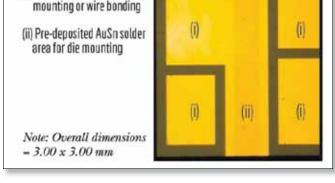

**FIGURE 2:** Advanced CVD diamond heat spreader design exhibiting a patterned metallization for a high-power laser-diode application

(i) Gold areas for component

## SOLUTIONS TO THERMAL ISSUES IN DEVICE PACKAGES FOR HIGH-END APPLICATIONS

To harvest the maximum heat-spreading effectiveness of diamond in the overall system design, package integration issues need to be carefully considered. Failure to address any one of these issues will result in a sub-optimal thermal solution. Here are the most important ones to be considered:

- Surface preparation

- Metallizations

- Mounting techniques

- Diamond thickness

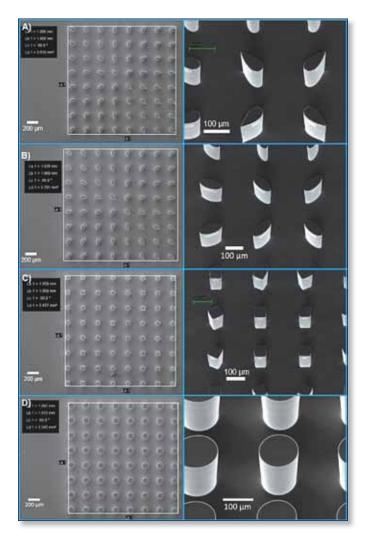

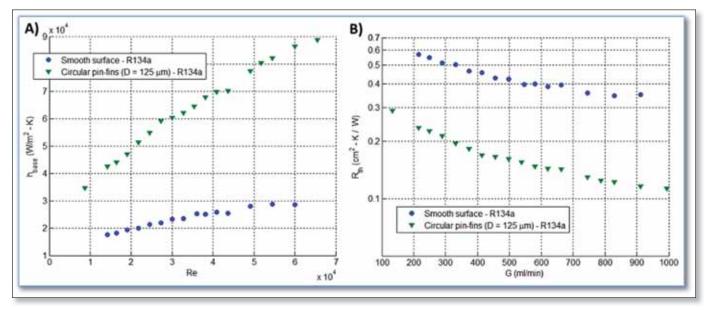

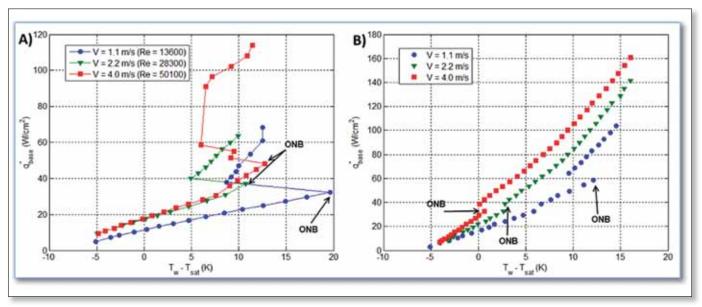

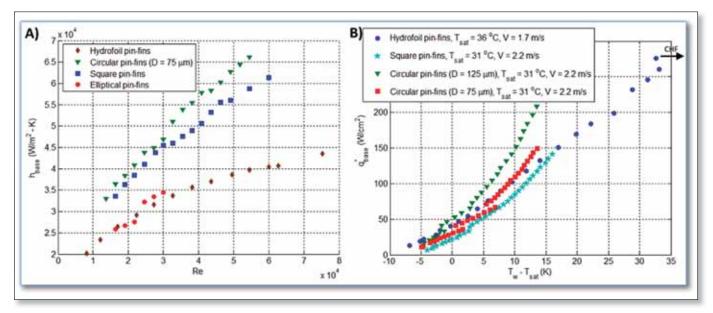

- Functional considerations.