THERMAL POWER PLANE ENABLING DUAL-SIDE ELECTRICAL INTERCONNECTS

Electronics

MARCH 2015 electronics-cooling.com

#### FEATURE

## CCA HEAT SINKS EMBEDDED WITH OSCILLATING HEAT PIPES

**BACK COVER**

INSIDE

DESIGN OPTIMIZATION OF A COLD PLATE

LIQUID IMMERSION IN THE DATA CENTER

BERGQUIST HIGH-PERFORMANCE LIQUID THERMAL INTERFACE MATERIAL

## With Bergquist Liquid Solutions, The Path You Take Is Yours.

#### Bergquist Highly Engineered Liquids Give You Complete Flexibility Over The Design And Delivery Of Your Thermal Solutions.

## Bergquist's full line of liquid polymers make it easy to customize your material, pattern, volume and speed.

Bergquist's advanced liquids are specifically designed to support optimized dispensing control with excellent thermal conductivity. Dispensed in a liquid state the material creates virtually zero stress on components. It can be used to interface and conform to the most

intricate topographies and multi-level surfaces. They are thixotropic in nature, helping the material to remain in place after dispensing and prior to cure. Unlike pre-cured materials, the liquid approach offers infinite thickness options and eliminates the need for specific pad thicknesses for individual applications.

Whether automated or hand dispensed, Bergquist liquid materials have natural tack and precisely flow into position for a clean final assembly with little or no stress on components.

#### Less stress, reduced application time with minimal waste.

Either manual, semi-automatic or automated dispensing equipment offers precise placement resulting in effective use of material with minimal waste. Boost your high volume dispensing needs by capitalizing on our expertise. Bergquist can help customers optimize their delivery process through its unique alignment with several experienced dispensing equipment suppliers.

#### Visit us for your FREE liquid samples.

Take a closer look at the Bergquist line of liquid

dispensed materials by getting your FREE sample package today. Simply visit our website or call us directly to qualify.

Request your FREE Liquid TIM Dispensed Sample Card

Call I.800.347.4572 or visit www.bergquistcompany.com/liquiddispense

18930 West 78th Street • Chanhassen, MN 55317 • TS 16949 Certified (800) 347-4572 • Phone (952) 835-2322 • Fax (952) 835-0430 • www.bergquistcompany.com

## **CONTENTS**

2 EDITORIAL Jim Wilson, Editor-in-Chief, March 2015

#### 4 COOLING MATTERS

News of Thermal Management Technologies

#### 6 CALCULATION CORNER

#### Strategies for the Thermal Modeling

of Metal Traces on Printed Circuit Boards Bruce Guenin, Assoc. Technical Editor

#### 12

#### **THERMAL FACTS**

Past Data and Columns Jim Wilson, Assoc. Technical Editor

36 COMPANY DIRECTORY

38 PRODUCTS & SERVICES

#### **FEATURE ARTICLES**

#### 14

#### DESIGN OPTIMIZATION OF A MULTI-DEVICE SINGLE-PHASE BRANCHING MICROCHANNEL COLD PLATE

Ercan M. Dede, Toyota Research Institute of North America

#### 24

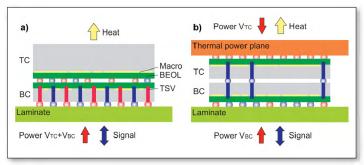

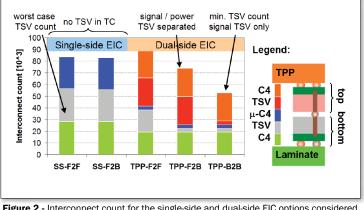

#### THERMAL POWER PLANE ENABLING DUAL-SIDE ELECTRICAL INTERCONNECTS FOR HIGH-PERFORMANCE CHIP STACKS

Thomas Brunschwiler, Gerd Schlottig, Hubert Harrer, Stefano Oggioni, IBM Research, IBM R&D, IBM Systems Supply Chain Engineering

30

#### LIQUID IMMERSION IN THE DATA CENTER: A MODULAR APPROACH FOR COOLING HIGH-PERFORMANCE MICROELECTRONICS

Joshua Gess, Sushil Bhavnani, Bharath Ramakrishnan, R. Wayne Johnson, Daniel Harris, Roy Knight, Michael Hamilton, Charles Ellis

#### 39 INDEX OF ADVERTISERS

#### CIRCUIT CARD ASSEMBLY HEAT SINKS EMBEDDED WITH OSCILLATING HEAT PIPES

Joe Boswell, Chris Smoot, Elliott Short, Nate Francis ThermAvant Technologies, LLC, Raytheon Company

## **Editorial** Encouraging and Investing

Jim Wilson, Editor-in-Chief, March 2015

Pelcome to our first edition of ElectronicsCooling in 2015. Most of us start a new year with reflection on the topics of goals and accomplishments. Even with our busy schedules and work demands, forcing ourselves to pause and consider career progress and aspirations is beneficial. A common method of reviewing your progress is to start with your accomplishments for the prior year. Listing some short and longer term goals helps focus your desires and align them with the needs of your employer. Another important part of this assessment process

is to identify training that would help you be a better and more productive employee. Following through with this training requires investment of time, effort, and money, usually from both the employee and employer. Investments like training usually have some expectation of a tangible return. For example, learning a new software program might make you more efficient or enable you to expand your design and analysis capability. Learning advanced testing techniques might prevent repeated errors in making measurements. For this editorial, I would like to encourage our readers to make some investments that have great return but are harder to quantify from a business perspective.

In the past few months I have been asked to write several letters of recommendation for friends and coworkers. Some of these were for technical awards and some for job promotions, and as of writing this editorial, a number of them have been awarded. While the recommendation letters are required as part of the nomination process, these individuals earned success with their accomplishments and hard work. Writing the letters was a nice diversion from my usually technical job and it has been rewarding seeing them receive their awards and promotions. Related, I have also increased my appreciation for those that encouraged and help me in the past.

As thermal engineers, much of our mental effort goes into managing complicated heat transfer processes and we can overlook opportunities to encourage others. Other barriers can come from the side effects of competition and confidence. An overly competitive environment can inhibit investing in others from a fear of making someone else even more competitive. Friendly competition is healthy and fosters even better ideas but should not prevent you from acknowledging others good work and input. Similarly, confidence in our work is required but overconfidence can hinder encouraging your teammates. I have come to truly appreciate coworkers that ensure everyone's contribution is acknowledged. They have learned to invest in relationships. Even if their relationship investments are not intended to have a response, I personally want to work harder for them. The environment set by an encouraging coworker also helps mitigate some of the stress that comes with working on challenging problems as a team.

Investing in coworker relationships extends beyond your immediate work environment. Technical conferences and meetings can be a good venue to collaborate and look for occasions to acknowledge the work of others. My personal opinion is that the some of the most valuable time spent at conferences is the interaction with colleagues during breaks discussing technical issues and fostering relationships.

A final challenge to you is to encourage your coworkers and invest in your professional relationships. It will be rewarding.

www.electronics-cooling.com

#### **ASSOCIATE TECHNICAL EDITORS**

Bruce Guenin, Ph.D. Principal Hardware Engineer, Oracle bruce.guenin@oracle.com

Madhusudan Iyengar, Ph.D. Member ASME, IEEE, ASHRAE, IMAPS miyengar@gmail.com

Peter Rodgers, Ph.D. Professor, The Petroleum Institute prodgers@pi.ac.ae

Jim Wilson, Ph.D., P.E. Engineering Fellow, Raytheon Company jsw@raytheon.com

#### PUBLISHED BY

ITEM Media 1000 Germantown Pike, F-2 Plymouth Meeting, PA 19462 USA Phone: +1 484-688-0300; Fax:+1 484-688-0303 info@electronics-cooling.com; electronics-cooling.com

#### **CONTENT MANAGER**

Belinda Stasiukiewicz bstas@item-media.net

MARKETING MANAGER Dawn Hoffman dhoffman@item-media.net

**GRAPHIC DESIGNER** Erica Osting eosting@item-media.net

#### EDITORIAL ASSISTANT

Allison Titus atitus@item-media.net

#### PRESIDENT

Graham Kilshaw gkilshaw@item-media.net

#### REPRINTS

Reprints are available on a custom basis at reasonable prices in quantities of 500 or more. Please call +1 484-688-0300.

#### SUBSCRIPTIONS

Subscriptions are free. Subscribe online at www.electronics-cooling.com. For subscription changes email info@electronics-cooling.com.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, or stored in a retrieval system of any nature, without the prior written permission of the publishers (except in accordance with the Copyright Designs and Patents Act 1988).

The opinions expressed in the articles, letters and other contributions included in this publication are those of the authors and the publication of such articles, letters or other contributions does not necessarily imply that such opinions are those of the publisher. In addition, the publishers cannot accept any responsibility for any legal or other consequences which may arise directly or indirectly as a result of the use or adaptation of any of the material or information in this publication.

Electronics Cooling is a trademark of Mentor Graphics Corporation and its use is licensed to ITEM. ITEM is solely responsible for all content published, linked to, or otherwise presented in conjunction with the Electronics Cooling trademark.

# Still Stuck?

Integrated thermal management solutions Navigated by Jones Tech PLC

Jones Tech PLC is engaged in providing creative solutions to improve the reliability of electronics equipment.

JONES TECH PLC (CHINA) No.3 Dong Huan Zhong Lu BDA.Beijing 100176, China JONES TECH LLC (USA) 19925 Stevens Creek Blvd., Suite 100 Cupertino, CA 95014, USA

## **Cooling Matters**

News of thermal management technologies

#### THERMALLY UNSUITABLE PRODUCT DROPPED FROM SAMSUNG PRODUCT LINE

**1/26/15** - Samsung reportedly dropped Qualcomm's Snapdragon 810 from its upcoming line of Galaxy S6 devices because Qualcomm's 20nm processors aren't running cool enough.

Samsung's reason for dropping the Snapdragon from its product line is extremely vague since it is well known that Qualcomms have been produced and sold in 20nm modems for more than a year.

It is unclear at this time how the drop will affect Samsung.

Source: Extreme Tech

#### LIQUID COOLING DECREASES ENERGY CONSUMPTION AND REDUCES FOOTPRINTS

2/2/15 - Icetope, a UK firm, partnered with Intel and the University of Leeds last year and launched a line of servers, which uses liquid cooling to cool electronics. The system, known as the PetaGen system, uses a combination of liquid coolants to cool electronics. Every motherboard is completely immersed in coolant inside a sealed container.

"The coolant is an exotic fluid called Novec developed by 3M, which is not electrically conductive and disperses heat from the components by convection. The blades fit into a rack-mount enclosure, with a separate cooling system in the rack that circulates water to remove heat from the blades. This arrangement enables a fully populated rack to mount up to 72 blade servers, each blade being a twin socket system based on the latest Intel Xeon E5-2600 v3 processors," according to V3.

The liquid cooling reduces the need for air condition in server rooms, which lowers energy consumption. Energy consumption is a common concern in data centers since the use of mobile devices is constantly growing and more data traffic comes online.

Source: V3

HIGH TEMPERATURE BRINGS DOWN DATA CENTER IN AUSTRALIA

1/19/15 - A heatwave that rose outside temperatures to 112 degrees Fahrenheit, brought

iiNet's data center down in Western Australia. The data center went offline due to equipment failures. Because servers can give off tremendous amounts of heat, the lack of sufficient cooling can lead to such cooling failures.

The record breaking temperature was the hottest day recorded in January since 1991. The high temperatures lead to an air conditioner failure, thus knocking the data center offline for more than six hours.

Heat bringing down data centers is very common; however, power infrastructure problems or cooling problems usually cause this occurrence, not outside weather.

"We have had multiple air conditioners fail on site causing temperatures to rise rapidly. We have additional cooling in now. We will begin powering services back up once the room has cooled adequately. If we are premature the room won't recover and risk the A/C failing again," Christopher Taylor, company representative, said.

Source: Data Center Knowledge

## **Datebook**

#### **MARCH 15-19 MARCH 15-19 MARCH 24-26** 2015 **SEMI-THERM 2015 Applied Power** 2015 Spacecraft FOR MORE EVENT **Thermal Control Electronics Conference** SAN JOSE, CALIF., U.S. **LISTINGS, VISIT** (APEC) 2015 http://www.semi-therm.org Workshop **ELECTRONICS-**CHARLOTTE, N.C., U.S. EL SEGUNDO, CALIF., U.S. http://www.apec-conf.org http://www.cvent.com COOLING.COM

#### THERMAL SIMULATION TO IMPROVE LED CAR HEADLIGHT DESIGN

**1/13/15** - Structural changes to LED headlights have generally been adding to the complexity of its production, according to researchers. Currently, the only constant in LED headlights is its thermal management.

CFD (computational fluid dynamics) simulation software is typically used to efficiently create prototypes of changes to LED headlights.

"The CFD analyst has to assign grids to the solids and flow spaces, creating an optimised computing mesh. This mesh aids the engineer in setting boundary conditions and influences the solution convergence as well as accuracy of the result," according to researchers.

Mesh generation for new lighting systems is very time consuming and details in the structures of headlights add to the complexity of this process. Researchers have discovered a solution – they believe LED car headlight designs can greatly benefit from thermal simulation.

Source: Electronics Weekly

#### NEED FOR HEAT SPREADERS YIELDS COOLING TECHNOLOGY

**1/6/15** - The Air Force Research Laboratory and a small business partner have announced they are developing technologies that will help electronics stay cool. With funding from the Air Force Small Business Innovation Research program, the AFRL expects to produce a technology that "will enable successful use of high-power processors that operate on satellites."

One of the technologies currently being tested is an OHP (oscillating heat pipe)-embedded micro-chip carrier that reduces the temperature of satellite components to manageable thermal levels. This is an advantage because it improves reliability and allows opportunity to increase onboard processing. This technology is currently being developed by ThermAvant Technologies, LLC in Missouri.

Source: AFRL

#### RESEARCH GROUP AT U-MICHIGAN DEVELOPS HEAT-CONDUCTING PLASTIC

**12/16/14** - A research team from the University of Michigan has developed a heat-conducting plastic that bends 10 times better than previous materials.

Plastic is a favorable material for electronic devices because it is lightweight, flexible and inexpensive. However, a known issue with plastic is its limited availability to dissipate heat. "The new U-M work could lead to light, versatile, metal-replacement materials that make possible more powerful electronics or more efficient vehicles, among other applications," according to researchers.

Source: University of Michigan

#### AIR FORCE FUNDS THERMAL MANAGEMENT PROJECT

**12/16/14** - The Air Force has provided over \$1.5 million dollars in funding to the Air Force Research Lab for an effort to improve methods of managing heat of electronics on fighter aircraft.

The goal of the project is to "enhance the technology and manufacturing readiness for nanoenhanced thermal interface material grease and to integrate it with power system modules that are currently used on advanced fighter aircraft."

"With further testing, the thermal interface material grease is expected to provide a 10 degrees Celsius or better reduction in junction temperatures. This reduction is expected to provide a direct increase in fuel cooling loop temperatures, improved end-of-mission thermal capability during ground idling, and improved reliability and cost savings," researchers said.

**Source: Greene County News**

#### **MAY 6-7**

Under-the-Hood Innov. Polymers and Thermal Mgmt. Conference

www.itbgroup.com

#### **JUNE 9-12**

Guangzhou International Lighting Exhibit GUANGZHOU, CHINA www.lightstrade.com

#### AUGUST 5-6

Advancements in Thermal Mgmt. 2015 DENVER, COLO., U.S. www.webcomcommunications.com

#### SEPTEMBER 29-31

SAE 2015 Thermal Management Systems Symposium TROY, MICH., U.S. http://saeevents.org

## Strategies for the Thermal Modeling of Metal Traces on Printed Circuit Boards

Bruce Guenin Assoc. Technical Editor

#### INTRODUCTION

S INTEGRATED CIRCUIT (IC) devices get more complex, the interconnections between them provided by printed circuit boards (PCBs) get more complicated as well. Thermal simulation software tools are getting more capable of importing PCB layouts and automating the process of creating a model of the PCB whose local thermal conductivity is representative of the underlying layout. However, in many cases it is necessary to perform a thermal model of a package on a PCB without creating a highly detailed model of a PCB. This article is the first of a series of columns that will explore the effectiveness of different strategies for accurately accounting for heat transfer into a PCB, while using a simplified solid model of the PCB.

#### **THERMAL MODEL**

The heat generated by an IC often has several flow paths into the PCB it is mounted to. Quite often in ball grid array (BGA) packages the central balls connect to vias in the PCB that route the heat directly into the power and ground planes in the PCB. In contrast, the peripheral balls tend to be connected to surface traces on the PCB. Some of the heat conducted by the traces flows directly into the ambient air. However most of it will flow to the interior of the PCB and enter the power and ground planes. These planes are typically effective in spreading the heat from a given package over a large area in the PCB, whence it can flow more efficiently into the ambient air.

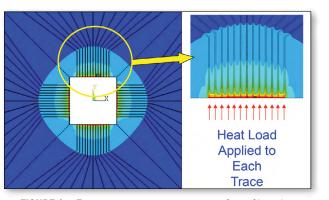

This analysis is devoted to exploring the heat transfer from the traces to the inner planes of the PCB. Any other heat flow path into the PCB is neglected in the model. The construction of the model is illustrated in Figure 1. The portion of the PCB where a package would normally be mounted has been removed. This exposes the cross-section of each of the traces at the periphery of the cutout. A heat flux is applied to the exposed surface of each trace. The magnitude of the heat flux to chosen so that a total of 1 W of heat is injected

FIGURE 1a - Temperature contour map, top surface of board.

collectively into all of the trace cross-sections. There are adiabatic boundary conditions at the exposed cross-section for each trace so that all the applied heat flows from that surface into the trace.

For convenience, the PCB geometry corresponds to that of a JEDEC-standard PCB, that would be used in the thermal testing of BGA packages [1]. The board consists of six layers: the top metal traces, two interior planes, and three

# One-Stop Show Sold States

Industries that we support: Cloud Computing Medical Equipment (MRI) Wind Power Solar Power Semiconductor Test Equipment Consumer Electronics Telecom

## Malico Inc. 2

:909-993-5140 E-mail : davidliang@malico.com :408-605-1616 E-mail : ky@maxpros.com :978-771-9285 E-mail : jhmclean@malico.com :214-514-9836 E-mail : annylo@malico.com Chino CA Tel , CA San Jose Mobile Mobile Boston MA TX Mobile Dallas FL Mobile :401-480-4752 E-mail : charlierandall@malico.com Tampa Website:www.malico.com

#### www.malico.con

o.com demark, are the properties where res dielectric layers. The board is 101 mm sq. and is 1.54 mm thick. The interior planes are 35  $\mu$ m thick. For reasons of test reproducibility, the traces on a JEDEC-standard PCB are 70  $\mu$ m. However, in PCBs used in products, a 35  $\mu$ m thickness is more common. Traces of both of these thickness values are analyzed in the model. The cutout in the PCB is 27 mm sq. Further details regarding the PCB construction may be found in a previous column [2].

A commercial finite element analysis (FEA) software tool was used to generate solid models of the multilayer board with a number of different trace configurations [3]. In all cases, the thermal solution was obtained assuming an ambient temperature of 0 °C (so that the reported temperatures represent T –  $T_{Ambient}$ ) and a heat transfer coefficient of 10W/m<sup>2</sup>K (typical of natural convection cooling) was applied to the top and bottom surfaces of the PCB.

The trace geometries are represented accurately in the model. Since the model was generated with an appropriately refined FEA mesh, the model results are assumed be "exact" when compared with the results of the models having simplified geometries.

Table 1 presents the various parameters characterizing the trace geometries for the three configurations studied. Each configuration has an "a" version and a "b" version. In all of the "a" versions, the trace thickness is 35  $\mu$ m. In all of the "b" versions, it is 70  $\mu$ m.

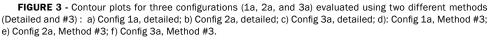

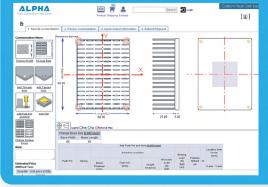

The images in Figure 3 illustrate the trace pattern of each configuration. [Note that a discussion of the thermal contours in this figure follows later in this article.]

#### SIMPLIFYING ASSUMPTIONS

It is common practice to represent the trace layer of a PCB as a continuous plane whose thickness equals that of the traces and whose thermal conductivity equals the copper coverage of the traces multiplied times the thermal conductivity of copper. This is commonly referred to as "smearing" the

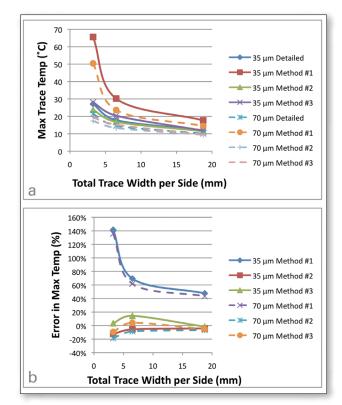

FIGURE 2 - Graphs depicting simulation results from Table 2 versus total trace width per side of the cutout in the parallel region of the traces: a) maximum trace temperature and b) error in maximum trace temperature.

trace layer. This procedure is defined herein to be Method #1 and is specified as:

• Simplification Method #1: represent trace layers by a plane. Plane thickness = trace thickness. Plane effective thermal conductivity = Factor x thermal conductivity of copper. Factor = % of PCB surface occupied by the traces.

All of the simplified models discussed here represent the trace geometry by a plane. However, they differ by the

| Table 1 - PCB Parameters |                    |                       |             |             |                                |                                  |                              |

|--------------------------|--------------------|-----------------------|-------------|-------------|--------------------------------|----------------------------------|------------------------------|

| Configuration<br>Number  | Trace<br>Thickness | Number<br>Traces/side | Trace Pitch | Trace Width | Sum of<br>Trace<br>Widths/side | %Cu in<br>Parallel<br>Trace Area | %Cu in<br>Entire PCB<br>Area |

|                          | (mm)               |                       | (mm)        | (mm)        | (mm)                           |                                  |                              |

| 1a                       | 0.035              | 13                    | 0.65        | 0.25        | 3.25                           | 38.5%                            | 3.2%                         |

| 2a                       | 0.035              | 13                    | 1.5         | 0.5         | 6.5                            | 33.3%                            | 6.1%                         |

| 3a                       | 0.035              | 25                    | 1           | 0.75        | 18.75                          | 75.0%                            | 16.7%                        |

| 1b                       | 0.070              | 13                    | 0.65        | 0.25        | 3.25                           | 38.5%                            | 3.2%                         |

| 2b                       | 0.070              | 13                    | 1.5         | 0.5         | 6.5                            | 33.3%                            | 6.1%                         |

| 3b                       | 0.070              | 25                    | 1           | 0.75        | 18.75                          | 75.0%                            | 16.7%                        |

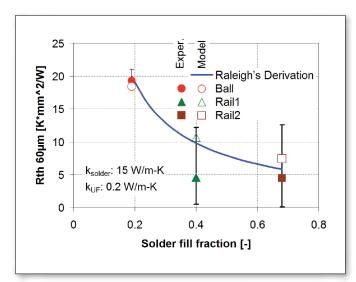

Table 1: Thermal conductivity of TPP laminate. The core laminate with annular vias from [12] is listed as benchmark case.

method used to calculate an effective thermal conductivity of the plane.

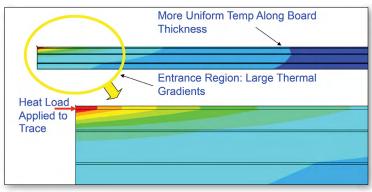

The thermal contour maps in Figure 1 indicate a significant thermal gradient in the traces as heat flows through them on their journey into the internal planes in the board. The side view also illustrates that the heat flows from the traces to the top plane of the PCB in a gradual way, due to the relatively low thermal conductivity of the board FR-4 dielectric (0.25 W/mK). The flow of heat from the traces to the plane is affected by the fact that the traces do not represent a continuous plane. Hence the heat flows, not uniformly over the full area of the dielectric, but is concentrated

in local regions, directly under each trace.

It should be noted also, that the temperature of the trace approximates that of the underlying plane after a distance equal to approximately 10 times the dielectric thickness. Hence, it is the portion of the traces near the package that make the most significant contribution to the heat flow between the traces and the top plane.

The insight gained by these observations leads to the formulation of two other methods of calculation of effective thermal conductivity values that represent a derating of the thermal performance of a smeared plane, that, otherwise, would provide a much more efficient thermal path to the top plane than do the individual traces.

- Simplification Method #2: represent trace layers by a plane. Plane thickness = trace thickness. Plane effective thermal conductivity = Factor x thermal conductivity of copper. Factor = % of PCB surface occupied by the traces near the package, where the traces are parallel.

- Simplification Method #3: represent trace layers by a plane. Plane thickness = trace thickness. Plane effective thermal conductivity = Factor x thermal conductivity of copper. Factor is calculated as in Method #2. The thermal conductivity of the dielectric between the inner plane and the top plane = Factor2 x thermal conductivity ity of the dielectric. Factor2 = trace width/trace pitch.

| Table 2 - Calculated Results                               |                    |           |           |           |           |           |           |

|------------------------------------------------------------|--------------------|-----------|-----------|-----------|-----------|-----------|-----------|

|                                                            | T,max Results      |           |           | % Error   |           |           |           |

| Configuration<br>Number                                    | Detailed<br>Traces | Method #1 | Method #2 | Method #3 | Method #1 | Method #2 | Method #3 |

|                                                            | (°C)               | (°C)      | (°C)      | (°C)      | (%)       | (%)       | (%)       |

| 1a                                                         | 27.2               | 65.6      | 23.8      | 28.1      | 142%      | -12%      | 3%        |

| 2a                                                         | 17.8               | 30.2      | 16.8      | 20.4      | 69%       | -6%       | 14%       |

| 3a                                                         | 12.0               | 17.7      | 11.5      | 11.8      | 48%       | -4%       | -2%       |

| 1b                                                         | 21.4               | 50.4      | 17.4      | 19.4      | 136%      | -19%      | -9%       |

| 2b                                                         | 14.6               | 23.7      | 13.3      | 15.2      | 62%       | -9%       | 4%        |

| 3b                                                         | 10.1               | 14.5      | 9.4       | 9.6       | 43%       | -7%       | -5%       |

| Assumptions: $T_{Ambient} = 0^{\circ}C$ . Total Power = 1W |                    |           | Average   | 83%       | -9        | 1%        |           |

Table 2: Thermal benchmarking of single-side and dual-side EICs. Characteristic elements are described in detail in [8].

Assumptions:  $T_{Ambient} = 0$  °C, Total Power = 1W Heat Transfer Coef. = 10W/m<sup>2</sup>K

#### **CALCULATED RESULTS**

The results of the calculations are detailed for all configurations in Table 2. The values of T,max for the 35  $\mu$ m configurations are all higher than the corresponding ones for the 70  $\mu$ m configurations, as expected. The values of T,max calculated using Method #1 are all higher than those calculated with the other methods. This should not be a surprise, since Table 1 indicates that the % copper averaged over the entire PCB surface is much lower that that calculated for the parallel trace region. For example, for configuration 3a and 3b, the % copper averaged over the parallel region is 75%, whereas the % copper averaged over the entire PCB is only 16.7%.

Methods #2 and 3 yielded values of T,max that are much closer to the exact values.

The graphs in Figure 2 depict the relative behavior of the different methods. Both the actual values of T,max and % error are plotted versus a parameter = total trace width per side = trace width x number of leads per side. Higher amounts of copper lead to larger values of this parameter. The graphs show that the accuracy of Method #1 improves at the higher copper levels. However, even at high copper levels, the error is still over 40%. At the lowest copper levels evaluated here, the error for Method #1 exceeds 100%.

There is much better performance with Methods #2 and #3. Averaged over all the cases studied here, Method #2 had -9% error and Method #3, 1%.

Figure 3 depicts selected temperature contour plots for all three configurations, version "a" (35 µm traces). The top row of images shows the results for the detailed trace models. The lower row depicts the results in which Method #3 was applied to the calculation of the effective thermal conductivity of the plane and the top dielectric. The values of T,Max were similar for the two approaches for each case. However, the detailed trace models clearly show the impact of the trace routing on the thermal gradients. The contours for Method #3 show, in general, more of a circular symmetry. [Note that the apparent presence of the traces in the lower set of images depicting Method #3 results is an artifact of using the same finite element mesh for all the solution methods applied to a particular PCB configuration. However, in the Method #3 models (as well as for #1 and #2) the same material properties were applied to all elements in the trace layer, making that layer truly isotropic in its thermal behavior.]

It was mentioned earlier that the assumed heat transfer coefficient equaled 10  $W/m^2K$ , representative of natural convection. It should be noted that, for higher values of the heat transfer coefficient, the tendency for the heat to be transferred from the traces to the top plane in the region near the package would be even more pronounced. This would be expected to further increase the error in applying Method #1.

#### CONCLUSIONS

Three different strategies for using a convenient "smeared" planar layer to represent a layer of discrete traces were explored. The strategies that were most successful were based on an understanding of the local heat transfer between the traces and the top plane in the PCB that was presented in an earlier column [2]. They made use of the fact that most of the heat transfer between the traces and the top plane of the PCB occurs near the package and that the heat flow is concentrated in the vicinity of each trace and does not flow uniformly through the dielectric. Hence, the copper coverage near the package should be used in calculating the effective thermal conductivity of the smeared plane and the thermal conductivity of the dielectric should be derated by the same factor. The conventional method, which uses a value of copper coverage averaged over the surface of the PCB is much less accurate.

#### REFERENCES

[1] See, for example: JEDEC Standard JESD51- 9, "Test Boards for Area Array Surface Mount Package Thermal Measurements," available for free download at www.jedec.org.

B. Guenin, "Entrance Effects for Heat Flow into a Multi-Layer Printed Circuit Board," ElectronicsCooling, Vol. 10, No. 4, November 2004.

[3] ANSYS<sup>®</sup>, Version15.0. High Power Semiconductor Lifetime Prediction, Failure Diagnosis and Thermal Performance Testing

## Graphics MicReD Industria 27 **^** P

## Introducing

## MicReD<sup>®</sup> Power Tester 1500A

A unique combination of Automated Power Cycling and Thermal Transient Measurement Technology

For MOSFET, IGBT and generic two-pole devices

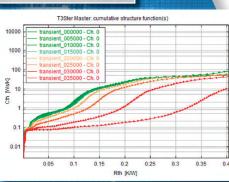

Non-Destructive Failure-in-progress Diagnosis Structure Function Analysis used to monitor degradation type and development by evaluation of the heat conduction path

Range of power cycling options

Touch Screen Interface operation suited to specialists and production staff

Up to 10x reduction in total testing time

Based on T3Ster<sup>®</sup> proven technology - Accurate Tj measurement - Repeatable evaluation of RthJC

> Technical Information: mentor.com/powertester-1500a

## Past Data and Columns

Jim Wilson Assoc. Technical Editor

lectronicsCooling magazine provided a technical data column from 1997 to 2009 with the intent of providing you, the readers, with pertinent material properties for use in thermal analyses. The most common materials and their associated thermal properties used in electronics packaging were covered. Table 1 lists a summary of the technical data columns divided into two categories, thermal conductivity and everything else. It is of note that thermal conductivity was the most frequent topic of interest. This is no surprise as thermal conductivity is one of the most difficult thermal properties to accurately measure. All of this data is accessible on our web site (www.electronics-cooling.com) which also includes all of the articles that have appeared in ElectronicsCooling.

Once most of the relevant thermal properties had been covered, the technical data column evolved into a "thermal facts and fairy tales" feature. This column has covered a variety of topics highlighting some of the typically overlooked or less understood characteristics of thermal management. Table 2 lists the columns in chronological order which are also available on our website. The range of topics suggests that thermal engineers often encounter complicated physics, especially when trying to match test data to predictions.

Our hope as editors is that you find these topics useful. We are always interested in feedback from our readers so feel free to contact us with your ideas and topics, especially if you have a particular thermal fact or fairy tale. This also provides an opportunity to remind the readers of how we work as an editorially independent publication. For each issue, one of the associate editors assumes the role of editor-in-chief and is responsible for either soliciting new technical articles or

selecting previously submitted articles that have gone through a review process and been judged worthy of publication. The review process requires at least two favorable evaluations from independent reviewers based on criteria including technical relevance and soundness, interest to our readership, absence of commercial content, and confirmation that the work has not been previously published. We frequently receive inquiries similar to "I could provide content along the lines of ..., would you be interested and/ or commit to publishing this?". While we welcome the dialogue, a typical response reminds the writer that we need an article to review and that we cannot commit to publication prior to the review process. However, we never want to discourage interest in publishing and we will certainly work with potential authors to help them develop their articles.

| Topic: Thermal Conductivity                                | Issue     | <b>Author</b> <sup>1</sup> |

|------------------------------------------------------------|-----------|----------------------------|

| Pure Metals                                                | Jan '99   | C.L.                       |

| Leadframe Materials                                        | May '97   | C.L.                       |

| Liquid Metals                                              | May '08   | C.L.                       |

| Alloys                                                     | Feb '07   | J.W.                       |

| Solders                                                    | Aug '06   | J.W.                       |

| Silicon (erratum in Sept '98: p12)                         | May '98   | C.L.                       |

| Various Silicon                                            | May '06   | C.L.                       |

| III-V Semiconductors                                       | Feb '06   | J.W.                       |

| Aluminum Oxide                                             | May '99   | C.L.                       |

| Ceramics                                                   | Sept '99  | C.L.                       |

| Composite Materials                                        | Jan '00   | C.L.                       |

| Pyrolytic Graphite                                         | Aug '02   | J.R.                       |

| Silicon Dioxide                                            | Aug '04   | C.L.                       |

| Unfilled Plastics                                          | May '01   | C.L.                       |

| The Anisotropic Thermal Conductivity of Plastics           | Aug '01   | J.R.                       |

| Filled Plastics                                            | May '09   | C.L.                       |

| Rubbers/Elastomers                                         | Nov '01   | C.L.                       |

| Thermal Insulators                                         | May '02   | C.L.                       |

| Fluids                                                     | Sept '00  | C.L.                       |

| Gases                                                      | Sept ' 98 | C.L.                       |

| Air                                                        | Feb '01   | C.L.                       |

| Air at Reduced Pressures and Length Scales                 | Nov '02   | C.L.                       |

| Moist Air                                                  | Nov '03   | C.L.                       |

|                                                            |           |                            |

| Various Topics                                             |           |                            |

| Heat Transfer Coefficients                                 | Jan '97   | C.L.                       |

| The Coefficient of Thermal Expansion I                     | Sept '97  | C.L.                       |

| The Coefficient of Thermal Expansion II                    | Jan '98   | C.L.                       |

| The Relationship Thermal-Electrical Conductivity           | May '00   | C.L.                       |

| Glass, Physical Properties and Categorization by Compounds | Feb '03   | J.R.                       |

| Thermal Capacitance                                        | May '03   | C.L.                       |

| Emissivity in Practical Temperature Measurements           | Aug '03   | J.R.                       |

| Surface Flatness                                           | May '04   | J.R.                       |

| Diamond, Synthesis and Physical Properties                 | Feb '02   | J.R.                       |

| Thin Wires: Criteria of Choice                             | Aug '05   | C.L.                       |

| Seebeck Coefficient                                        | Nov '06   | C.L.                       |

| Phase Change Materials                                     | May '05   | J.W.                       |

| Thermal Diffusivity                                        | Aug '07   | J.W.                       |

| Thermal Effusivity                                         | Nov '07   | C.L.                       |

| Title                                                                                                                                                                                                                 | Issue     | Author <sup>1</sup> |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------|--|--|

| Most of Us Live Neither in Wind Tunnels nor in the World of Nusselt                                                                                                                                                   | April '10 | C.L.                |  |  |

| Uncertainty is Assured                                                                                                                                                                                                | July '10  | J.W.                |  |  |

| Fully Developed Channel Flow: Why is Nu Constant?                                                                                                                                                                     | Sept '10  | C.L.                |  |  |

| Fixed Temperature and Infinite Heat Sinking                                                                                                                                                                           | Dec '10   | J.W.                |  |  |

| Published Thermal Conductivities Values:<br>Facts or Fairy Tales                                                                                                                                                      | Mar '11   | C.L.                |  |  |

| Consistency and Accuracy in Simulations                                                                                                                                                                               | June '11  | J.W.                |  |  |

| Does Your Correlation Have an Imposed Slope?                                                                                                                                                                          | Sept '11  | C.L.                |  |  |

| Heat Sinks, Heat Exchangers, and History                                                                                                                                                                              | Nov '11   | J.W.                |  |  |

| Heat Spreading Revisited                                                                                                                                                                                              | Mar '12   | C.L.                |  |  |

| Time Dependent Responses and Superposition                                                                                                                                                                            | June '12  | J.W.                |  |  |

| The Temperature Dependence of the Specific Heat                                                                                                                                                                       | Sept '12  | C.L.                |  |  |

| Not Always Efficient                                                                                                                                                                                                  | Dec '12   | J.W.                |  |  |

| Are Critical Heat Fluxes of LEDs and ICs<br>Comparable                                                                                                                                                                | Mar '13   | C.L.                |  |  |

| A System Perspective for Electronics Cooling                                                                                                                                                                          | June '13  | J.W.                |  |  |

| How Useful are Heat Sink Correlations for<br>Design Purposes                                                                                                                                                          | Sept '13  | C.L.                |  |  |

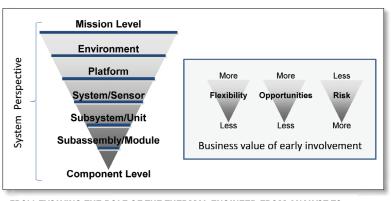

| Evolving the Role of the Thermal Engineer from<br>Analyst to Architect                                                                                                                                                | Dec '13   | Guest<br>Authors    |  |  |

| Historical Suggestions for Thermal Management of Electronics                                                                                                                                                          | May '14   | J.W.                |  |  |

| Virtual Prototyping                                                                                                                                                                                                   | Sept '14  | P.R.                |  |  |

| Moist Air and Cooling Electronics                                                                                                                                                                                     | Dec '14   | J.W.                |  |  |

| <sup>1</sup> C.L. = Clemens J.M. Lasance, Associate Editor, Philips Research Laboratories<br>J.W. = Jim Wilson, Associate Editor, Raytheon Company<br>P.R. = Peter Rodgers, Associate Editor, The Petroleum Institute |           |                     |  |  |

TABLE 2: Thermal Facts and Fairy Tales

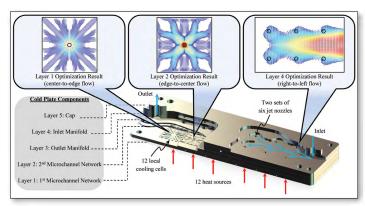

**FROM A SYSTEM PERSPECTIVE FOR ELECTRONICS COOLING:** June 2013 - Microchannel cooling for an IC

#### TABLE 1: Technical Data

Emissivity in Practical Numerical Modeling

<sup>1</sup>C.L. = Clemens J.M. Lasance, Associate Editor, Philips Research Laboratories

J.R. = Jukka Rantala, Associate Editor, Nokia Research Center J.W. = Jim Wilson, Associate Editor, Raytheon Company

Viscosity

**Building Materials**

Heat of Vaporization

Antifreeze Coolants

To view all past columns, visit www.electronics-cooling.com.

May '07

Feb '08

Aug '08

Nov '08

Feb '09

C.L.

J.W.

J.W.

C.L.

J.W.

## **Design Optimization of a Multi-Device Single-Phase Branching Microchannel Cold Plate**

Ercan M. Dede Toyota Research Institute of North America

#### INTRODUCTION

**INGLE-PHASE LIQUID COOLING** is an established approach to the thermal management of highly-reliable hybrid vehicle power electronics. However, as the electrification of hybrid vehicles increases, and under-hood space becomes further constrained, semiconductor device power densities continue to rise (in excess of 200 W/cm<sup>2</sup>) resulting in significant thermal management challenges. In response to this trend, there is sustained interest in the development of more compact, higher-performance cold plates for single-phase liquid cooling.

Fractal or branching microchannel flow networks have been identified to offer several advantages including low flow resistance [1], reduced channel wall temperatures [2], and greater overall cold plate temperature uniformity [3]. Generally, these performance benefits equate to lower system pumping power and better electronics temperature regulation. At the same time, a strategy to increase heat transfer in a more compact space is to stack multiple coolant channel layers for increased surface area and reduced unit thermal resistance [4, 5].

Building off of these two research directions, a single-device multi-pass branching microchannel heat sink was developed previously through the use of numerical gradient-based optimization techniques [6]. In this article, the design optimization of a related single-phase cold plate for the cooling of 12 large-area planar devices is briefly reviewed, and the fabrication and experimental testing of a prototype structure is described. The single-device cold plate geometry considered in [6, 7] is exploited as a periodic cooling cell in the development of a larger multi-device cooler, as described in [8], that also incorporates optimized global inlet and outlet manifold structures.

**Ercan M. Dede** received his B.S. degree and Ph.D. in mechanical engineering from the University of Michigan and a M.S. degree in mechanical engineering from Stanford University. Currently, he is a manager in the Electronics Research Department at the Toyota Research Institute of North America. His group conducts research on advanced vehicle electronics systems including power semiconductors, advanced circuits, packaging, and thermal management technology. He has over 20 issued patents and more than 30 articles in archival journals and conference proceedings on topics related to design and structural optimization of thermal, mechanical, and electromagnetic systems. He is an author of a recently published book entitled 'Multiphysics Simulation: Electromechanical System Applications and Optimization.'

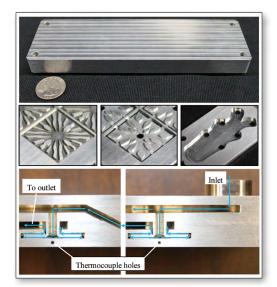

#### **COLD PLATE DESIGN AND FABRICATION**

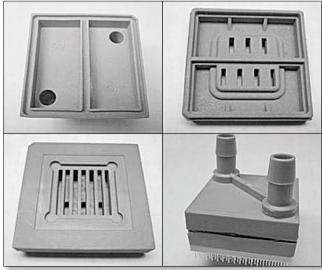

A sectioned perspective view of the multi-layer branching microchannel cold plate is shown in Fig. 1, where 12 local cells are placed in a periodic array for the cooling of multiple electronic devices; a cooling cell comprises microchannels arranged into two (Layer 1 and Layer 2) heat exchange passes. The optimal coolant flow paths used to develop the cold plate geometry are shown in the upper images of Fig. 1 using normalized fluid velocity vectors; note that larger velocities are shown in red. The branching channel flow maps, upper left and center images in Fig. 1, are obtained using a multiphysics topology optimization technique [6, 7], where the channel networks are found by minimizing an objective function comprising two terms related to the average temperature and fluid power dissipated in an assumed design domain. The optimization results serve as templates in the synthesis of the Layer 1 and Layer 2 microchannel designs. Alternatively, the Layer 3 (outlet) and Layer 4 (inlet) manifolds with wavy wall shape, upper right image in Fig. 1, are optimized for uniform fluid flow to the local cooling cells with minimum pressure drop [8, 9].

In the lower image in Fig. 1, the blue arrows indicate that the coolant enters through the vertical inlet of the cold plate at the right end. The coolant then travels horizontally through the inlet manifold and is evenly distributed in parallel via the first six jet nozzles to local microchannel cooling cells. From there, the coolant flows into the local

Figure 1 - Sectioned perspective view of multi-pass branching microchannel cold plate for cooling 12 electronic devices (lower image © [2014] IEEE. Reprinted, with permission, from [8]). Normalized fluid velocity vector flow maps (upper images) from structural optimization studies [6-9] with larger velocities indicated in red.

Layer 1 (outward flowing) branching microchannel system. The coolant then reverses direction to flow radially inward through the Layer 2 branched microchannel network. Finally, the heated coolant empties into the Layer 3 outlet manifold, and the entire process repeats as two sets of six local cooling cells are connected in series to increase the flow rate to all cells.

The cold plate dimensions are 50 mm x 150 mm x 12.5 mm. Each jet nozzle diameter is 2.5 mm. The third and fourth layer manifold fluid passages are 2.54 mm in height. Layers 1 and 2 have microchannels that are 0.5 mm in height. Each local cooling cell covers a footprint area of 20 mm x 20 mm.

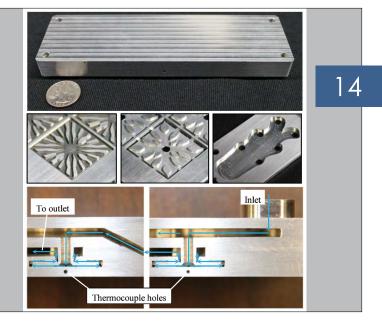

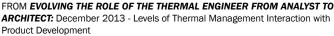

The cold plate is fabricated out of aluminum by precision machining the individual layers and diffusion bonding them to arrive at a unified structure [7]. The end result is a cold plate with minimal interfacial thermal resistance. Figure 2 illustrates the final assembled cold plate with zoomed views of the as-built microchannel/manifold geometry (middle row images) and cross-section (lower row images). The cross-section views show the inlet region of the cold plate (lower right) and a middle section of the cooler (lower left), where the blue arrows denote the coolant flow path and highlight the global flow transition from the first set of six cooling cells to the second set of six cells. Observe in Fig. 2 that a short microchannel height minimizes fin/channel distortion, and the diffusion bonding technique results in a continuous thermal path through the thickness of the assembly. Embedded thermocouple instrumentation holes are centered directly below each local cooling cell jet orifice.

#### **EXPERIMENTAL FACILITY AND PROCEDURE**

The experimental facility used for measuring the performance of the cold plate consists of a recirculating chiller, in-line filter, rotary style flow meter, and test section. A standard 50/50 ethylene-glycol/water mix is used in all experiments. The test section comprises a 12-device heater assembly attached to the cold plate plus associated temperature and pressure

**Figure 2** - Fully assembled cold plate (upper image). Zoomed views of Layer 1 and Layer 2 microchannels plus manifold geometry (middle images from left to right, respectively). Zoomed cross section views of the inlet region with a single cooling cell (lower right image) and the middle transition region with a second cooling cell (lower left image). The blue arrows in the lower images indicate the coolant flow path. © [2014] IEEE. Reprinted, with permission, from [8]

drop measurement instrumentation. Flow test connectors are utilized to interface with the cold plate and provide for coolant inlet and outlet temperature measurements. A differential pressure transducer is attached to the cold plate via additional taps positioned just after the flow test connectors.

Twelve aluminum nitride ceramic (250 W, 9.4 mm square) resistive devices are solder bonded to a specially designed 3.18 mm thick copper (Cu) plate for the heater assembly, which is bolted to the cold plate with a thermal interface material (TIM) grease layer in between. To determine power dissipation accurately, each device is wired in series to a shunt resistor for precise device voltage drop measurement. Each device/ resistor arm is wired in parallel to a 1.4 kW power supply. Temperature measurements are acquired for each local cooling cell using calibrated thermocouples located as shown in Fig. 2. Heater assembly temperatures on the opposite side of the TIM interface are measured at the mid-plane of the Cu plate using thermocouples positioned in line with the cold plate thermocouples. Using a calibrated infrared (IR) camera, the device temperatures are additionally measured; note that the heater assembly is coated with high emissivity flat black paint for accurate thermal imaging.

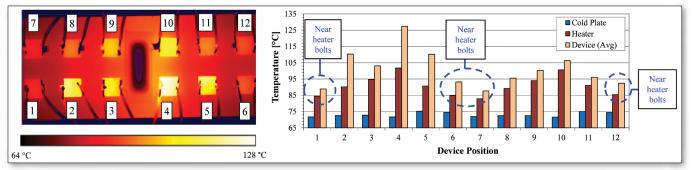

Steady-state thermal-fluid performance of the cold plate is evaluated over multiple test runs at an elevated coolant inlet temperature. Coolant flow rates ranging from 0.5 to 2.5 l/min in 0.5 l/min increments are used. The supplied heater power is adjusted at each flow rate to achieve a maximum heater device temperature of ~125 °C (as verified via IR camera). Additional details regarding the test setup and experimental procedure are found in [8].

#### **EXPERIMENTAL RESULTS**

Figure 3 shows a representative thermal image of the heater assembly and devices taken at the maximum coolant flow rate of 2.5 l/min. The corresponding bar chart in Fig. 3 shows the experimentally measured cold plate, heater plate, and device average temperatures for each numbered cell in the IR image. The bar chart indicates that the cold plate temperatures are uniform to within 3.6 °C. A periodic trend in the heater temperatures is observed between the first row of device positions (i.e., 1-6) and the second row of positions (i.e., 7-12). Logically, heater temperatures closer to the bolts (i.e., positions 1, 6, 7, and 12) exhibit lower values due to reduced grease layer thermal resistance and possible heat sinking effects from the bolts. In Fig. 3, device 4 limits the total input power to the system with a maximum temperature of 127.4 °C. Positions 2, 4, and 5 have a larger temperature differential between each device average temperature and corresponding heater temperature indicating that the large-area solder bond layers for these devices likely contain well-known process-induced voids [10] leading to increased thermal resistance; see [8] for additional discussion.

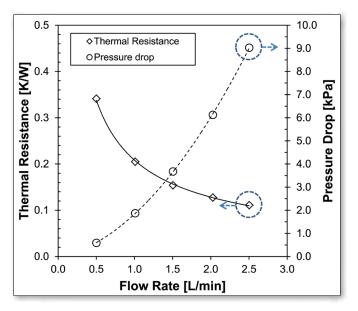

After post-processing the experimental data by calculating the device power and performing a system energy balance, the cold plate convective thermal resistance is determined. Specifically, the device power is found by calculating the current using the known shunt resistance and corresponding measured voltage drop. A system energy balance is then performed to determine the power lost to the ambient environment (i.e., power in minus power out). The total input power to the system is the sum of the measured power to each device. The power carried out of the system by the coolant is determined using the known coolant specific heat capacity, measured coolant outlet-to-inlet temperature difference, and measured system mass flow rate. The thermal resistance of each cooling cell is then calculated by dividing the measured cold plate temperature minus coolant inlet temperature difference by the known device power (adjusted for power losses). The inlet temperature to the entire cold plate is used to calculate the thermal resistance of the first six cooling cells, while the inlet temperature to the second set of six cooling cells is specified as the cooler inlet temperature plus one-half of the rise in liquid temperature as measured from inlet to outlet. The reader is referred to [8] for additional details.

In Fig. 4, the cold plate thermal resistance (primary vertical axis) and experimentally measured pressure drop (secondary vertical axis) is shown as a function of flow rate with added trend lines. The pressure drop data in Fig. 4 is averaged over two test runs, while the thermal resistance data is further averaged across all 12 cooling cells. A maximum average cold plate thermal resistance of 0.341 K/W with a minimum average pressure drop of 0.59 kPa was determined at the lowest tested flow rate of 0.5 l/min. In contrast, a minimum average thermal resistance of 0.112 K/W with a maximum average pressure drop of 9.03 kPa was measured at the highest flow rate of 2.5 l/min. Explanation of experimental uncertainties and additional design performance verification by simulation is provided in [8].

Direct comparisons of cold plate performance are often challenging due to differences in the end application including the number of power devices, selected coolant, coolant flow conditions, cold plate material selection, and cooler size/packaging constraints. However, a recent investigation of advanced liquid cooling strategies for a representative traction drive application may be used for rough comparison. Specifically, a definition of coefficient of performance (COP) similar to [11] is assumed using only convective thermal resistance. Furthermore, the parallel operation of two branching microchannel cold plates is assumed for cooling approximately the same number of power devices. Based on these assumptions, the multi-pass branching microchannel cold plate is estimated to have a COP comparable to submerged jet-impingement on a microfinned enhanced copper surface, thus outperforming a traditional aluminum channel-flow cooling approach [11]. Here, a COP benefit for the branching microchannel cold plate is realized through relatively low pressure drop at a reduced flow rate.

#### CONCLUSIONS

This article provided the design and fabrication details of a unique compact multi-device branching microchannel cold plate developed for hybrid vehicle electronics. An experimental facility for measuring thermal-fluid performance was briefly described. Thermal resistance and pressure drop test results were outlined, and the presented cold plate design exhibits favorable performance.

Figure 3 - Representative IR thermal image (on left) from first experimental run at a coolant flow of 2.5 l/min. Bar chart (on right) of cold plate, heater plate, and device average temperatures corresponding to the same test run. © [2014] IEEE. Reprinted, with permission, from [8]

Figure 4 - Cold plate thermal resistance (average of 12 local cooling cells over two test runs) and pressure drop (average over two test runs) shown with trend lines as a function of flow rate.

While the multi-layer construction with remote cooling strategy presented here necessitates diffusion bonding, more integrated layered designs may be achieved at the electronics substrate or semiconductor device level using well established etching and deposition micro-fabrication techniques. Furthermore, the emergence of additive manufacturing technologies may further facilitate direct adoption of more complex threedimensional cooling strategies in future electronics systems.

From a design perspective, related optimization techniques may be applied broadly to address a variety of topics including, for example, liquid manifold design for two-phase cooling, heat sink design for air cooling, and composite microstructure design for heat flow control in electronics [9]. Thus, the use of optimization methods in the early stages of the product development process holds promise as an approach to the creation of highly efficient electronics thermal energy management solutions.

#### REFERENCES

[1] Bejan, A., "Constructal tree network for fluid flow between a finite-size volume and one source or sink." Revue Ge´ne´rale de Thermique, 36(8), pp. 592–604, 1997.

[2] Pence, D., "The simplicity of fractal-like flow networks for effective heat and mass transport." Experimental Thermal and Fluid Science, 34(4), pp. 474–486, 2010.

[3] Wang, X.-Q., Mujumdar, A.S., and Yap, C., "Thermal characteristics of tree-shaped microchannel nets for cooling of a rectangular heat sink." International Journal of Thermal Sciences, 45(11), pp. 1103–1112, 2006.

[4] Vafai, K., and Zhu, L., "Analysis of two-layered micro-channel heat sink concept in electronic cooling." International Journal of Heat Mass Transfer, 42(12), pp. 2287–2297, 1999.

[5] Wei, X., and Joshi, Y., "Stacked microchannel heat sinks for liquid cooling of microelectronic components." Journal of Electronic Packaging, 126(1), pp. 60–66, 2004.

[6] Dede, E.M., "Optimization and design of a multipass branching microchannel heat sink for electronics cooling." Journal of Electronic Packaging, 134(4), p. 041001 (10 pages), 2012.

[7] Dede, E.M., and Liu, Y., "Experimental and numerical investigation of a multi-pass branching microchannel heat sink." Applied Thermal Engineering, 55(1–2), pp. 51–60, 2013.

[8] Dede, E.M., "Single-phase microchannel cold plate for hybrid vehicle electronics." 30th Annual Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM 30), pp. 118–124, March, 2014.

[9] Dede, E.M., Lee, J., and Nomura, T., Multiphysics Simulation: Electromechanical System Applications and Optimization, Springer, London, 2014.

[10] Ciappa, M., "Selected failure mechanisms of modern power modules." Microelectronics Reliability, 42(4–5), pp. 653–667, 2002.

[11] Waye, S.K., et al., "Advanced liquid cooling for a traction drive inverter using jet impingement and microfinned enhanced surfaces." 2014 IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), pp. 1064–1073, May, 2014.

## SIMULATING SYSTEMS

FLOW – THERMAL – STRESS – EMAG – ELECTROCHEMISTRY – CASTING OPTIMIZATION REACTING CHEMISTRY – VIBRO-ACOUSTICS MULTIDISCIPLINARY CO-SIMULATION

FULL DETAIL COMPLETE PHYSICS EXPLORE ALL DESIGN POSSIBILITIES

## **Circuit Card Assembly Heat Sinks Embedded** With Oscillating Heat Pipes

Joe Boswell<sup>1</sup>, Chris Smoot<sup>1</sup>, Elliott Short<sup>2</sup>, Nate Francis<sup>2</sup> <sup>1</sup>ThermAvant Technologies, LLC <sup>2</sup>Raytheon Company

#### INTRODUCTION

**N THIS STUDY**, lightweight two-phase heat sinks embedded with the Oscillating Heat Pipe (OHP) technology are developed for the thermal management of military circuit card assemblies (CCA). OHP-embedded heat sinks efficiently transport heat generated by CCA centrally located components to the assembly's edges. Attention is paid to minimize the size, weight, cost and potential operability penalties associated with the incorporation of the OHP-embedded heat sink, to improve upon existing high performance heat sinks (e.g., Al-Be composites,

**Joe Boswell** is co-founder and CEO of ThermAvant Technologies where he leads the firm's general affairs and has been Principal Investigator on a half-dozen government sponsored heat transfer research efforts. Prior to ThermAvant, Mr. Boswell was the founding CFO of InsideTrack, Inc. and before that an investment banker at JPMorgan's M&A Group. He is a graduate from the University of Pennsylvania's dual-degree M&T program; a member of the Association of Energy Engineers and ASHRAE; LEED EB certified; and co-inventor of ThermAvant's one approved and three pending patents.

**Dr. Christopher Smoot** (Senior Thermal Engineer, ThermAvant) leads many of ThermAvant Technologies' mechanical and thermal design efforts including finite element modeling and computational fluid dynamics simulations. In 2013, Christopher earned his PhD at University of Missouri-Columbia. Christopher has authored or co-authored seven publications related oscillating heat pipes including "Experimental Investigation of a Three-Layer Oscillating Heat Pipe, 2014, ASME Journal of Heat Transfer, "Thermal and Visual Observation of a Hybrid Heat Pipe," 2013, Heat Transfer Research, and "Robust Thermal Performance of a Flat-Plate Oscillating Heat Pipe during High-Gravity Loading," 2011, ASME Journal of Heat Transfer.

**Dr. Elliott Short** is a Raytheon Engineering Fellow responsible for designing, developing, and testing thermal management systems. He earned a BSME from the University of Texas at Austin in 1973, a MS in Mechanical Engineering and a MS in Aeronautical Engineering from the University of Arizona in 1977, and a Ph.D. in Mechanical Engineering at SMU in 1994. He is a registered Professional Engineer in Texas, an ASME Fellow, and an AIAA Associate Fellow.

encapsulated annealed pyrolitic graphite, or outfitted with Copper-Water heat pipes). This article provides a brief update on current OHP technology and summarizes initial findings from prototype OHP-embedded heat sinks.

#### BACKGROUND

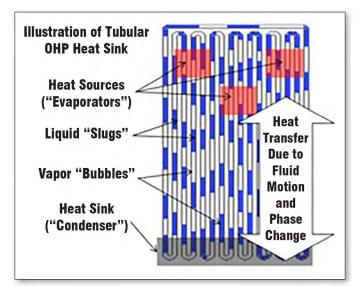

OHPs (or Pulsating Heat Pipes, PHPs), Figure 1, were invented by Akachi in 1990 [1] and first considered for adoption in electronics cooling applications in the early 2000's [2]. They are passive two-phase cooling devices made from capillary-sized tubing that meanders in a closed- or open-loop channel pattern. This channel pattern is evacuated and partially charged with a working fluid and hermetically sealed. Heat is transferred by the working fluid's latent and sensible heat as vapor bubbles expand, contract, and in turn oscillate the liquid slugs. No wick structures are involved. OHP-embedded heat sinks have proven capable of transporting kilowatt-level heat loads at effective thermal conductivities greater than 30kW/m-K [3]; and have proven reliable when operating in adverse gravity fields (e.g. up to 10g) [4]. Despite these attractive features, OHPs are not yet widely applied in electronics thermal management due to: perceived high costs, lack of predictability or information regarding reliability, and difficulty functioning at low temperature differentials (e.g., less than 15°C) [5].

## INTRODUCING **COOLSPAN® TECA** thermally & electrically conductive adhesive

#### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

#### CONTACT YOUR SUPPORT TEAM TODAY

## **MEET YOUR COOLSPAN® TECA FILM SUPPORT TEAM**

Leading the way in... • Support • Service • Knowledge • Reputation

#### SCAN THE CODE TO GET OUR CONTACT INFO.

Dale Doyle Applications Manader Territorv

Scott Kennedy

John Hendricks Regional Sales Manager

Kent Yeung Regional Sales Director

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

#### HEAT TRANSFER MECHANISM

While OHPs are passive cooling devices, they operate like active, fluid-pumped devices wherein the kinetic energy of the fluid comes from the thermal energy of the heat source(s) themselves. When at rest (i.e., uniform temperatures across the unit), a well-designed OHP distributes its working fluid as a chain of liquid slugs and vapor bubbles throughout its channel pattern. OHPs start-up when a temperature differential is applied by heat sources (or heat sinks) and cause partial evaporation of nearby slugs (or condensation of bubbles). The fluid's phase change results in volume and pressure differentials which in turn force the slugs and bubbles from relatively warm, high pressure areas (evaporators) toward cooler lower pressure ones (condensers) where a portion of the incoming bubbles condense, reject latent heat, and contract. The relatively cool fluid originally in the condensers is dislodged toward the evaporators through the channel pattern's 180-degree turns. These movements disrupt (or oscillate) the working fluid chain, and new liquid slugs move into the evaporators, and

the cycle repeats. Thus, OHPs utilize both the sensible (liquid flow) and latent (evaporation and condensation) heat of the working fluid. OHPs sustain this dual-mode heat transfer as long as the high-frequency phase change events continually disturb the system's equilibrium; and working fluid temperature is sufficiently above its triple point (to maximize saturation pressure differentials and minimize liquid viscosity and density) yet below its critical point (to maximize surface tension and volume differentials of phase change events).

#### MANUFACTURABILITY

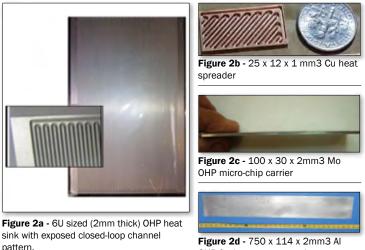

Ongoing research and development is being conducted not only on OHP design and modeling but also on reliable, affordable production methods to manufacture OHPs that are integral to the base material and delivered in either flat plate and/or three-dimensional form factors. OHPs have been successfully built with thicknesses vary-

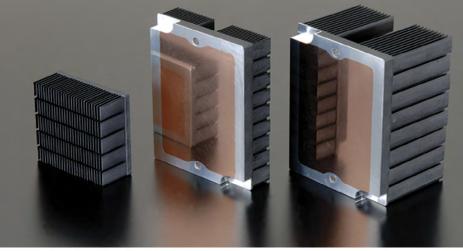

ing from 0.75mm (0.030") to 40mm (0.25"); lengths ranging from 25mm (1") to greater than 750mm (30"); manufactured from a variety of materials including Al, Cu, Ti, Mo, AlN, *etc.*; and paired with working fluids including water, acetone, common HCFCs, and nano-fluid derivatives of such fluids. Most lab-scale OHPs are made from meandering tubing that is sealed and charged with working fluid; however real-world applications require the OHP to be embedded into a flat-plate, Figure 2, or an even more complex three-dimensional shapes.

#### DESIGN AND PREDICTABILITY

An all encompassing mathematical model of OHPs' underlying thermo-physical events that enable their fluid oscillations and high heat transport capabilities has been an elusive goal of researchers since Akachi's invention 25 years ago [7-13]. To manage the scope of this article, a brief introduction of key

Figure 1 - Illustrated OHP with a chain of liquid slugs and vapor bubbles inside an 8-turn, closed-loop channel pattern.

Figure 2d - 750 x 114 x 2mm3 Al OHP for heat recovery unit

OHP design variables and a simplified method for estimating the affects of embedding an OHP inside a thermal module's base material are presented.

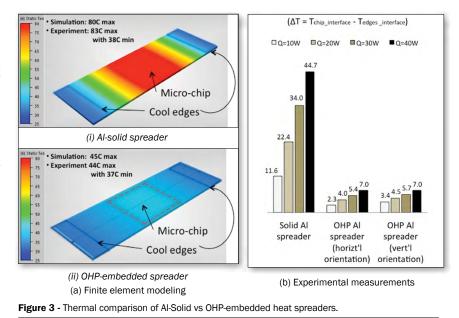

Two primary factors in designing an OHP are: 1) working fluid selection; and 2) channel pattern design. The working fluid is selected based on its thermophysical properties, compatibility with desired heat sink material, and the heat sink's expected operating conditions (e.g., temperatures, heat loads, gravitational fields, *etc.*). Functional charging ratios vary from 10% to 90% of the OHP channel pattern's empty volume [6]. The OHP's channel pattern design considerations include: geometric constraints (e.g. external dimensions, through holes, *etc.*); turn-number [14]; relative location of heat source(s) and sink(s); manufacturing methods available for selected material; and (most notably) channel diameter such that the working fluid's surface tension [15] and wetting of the material's walls [16] maintain the chain of discrete liquid slugs and vapor bubbles. Once the OHP designer has completed selection of the working fluids, design of the internal channel pattern, and numerical modeling of the OHP's evaporator-to-condenser thermal resistance (if such modeling is practical), a simplified Finite Element Modeling (FEM) approach can be used to estimate the OHP's impact on the application's overall thermal resistance. For steady-state modeling, the key thermal properties to customize are axial and radial thermal conductivities (k<sub>thermal</sub>) which can be deduced from the finite element model - or by referencing empirical results from similar OHP-embedded applications. Figure 3a is an example of how a simplified FEM approach can be used to reasonably predict an OHP's effect on a module's thermal performance. Figure 3(a,i) shows the predicted steady state temperatures of a solid Al heat

spreader with three-dimensional kthermal of 167W/m-K; and figure 3(a.ii) an OHP-embedded Al heat spreader of equal dimensions and base material but embedded with a channel pattern with an axial-wise kthermal 5kW/m-K and a radial kthermal of 1W/m-K. Both units were simulated when attached to a 40W central heat source and two cold blocks at the units' distant edges. Simulations predicted solid Al heat spreader maximum temperature of 80°C (or 44°C above its cold block interface); and the OHP-embedded unit's maximum temperature of 45°C (or 7°C above its cold block interface). Prototype units were then fabricated and experimentally measured with a centrally located heat source and two cold blocks on each edge to match the operating conditions used in the simulations. The OHP unit was tested in both horizontal and vertical orientations to evaluate performance through a 1g field. Experimental results presented in Figure 3(b) closely match FEM predictions: at 40W of input heat, the solid Al unit's measured maximum temperatures varied from 83-84°C (45°C above its cold block interface temperatures); and the OHP unit's measured maximum temperatures were 44-45°C (7°C above its cold block interface temperatures) in both horizontal and vertical orientation. This modeling approach has proven predictive in other development efforts, including CCA heat sinks.

#### FIELDED APPLICATION

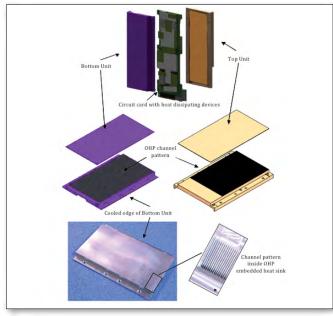

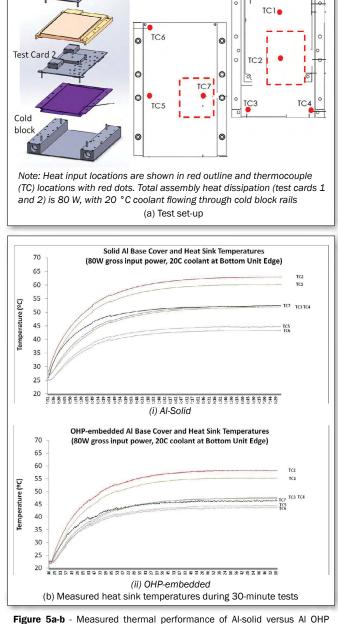

Based on the OHP's inherent thermal features and recent manufacturing and design advancements, prototype OHPembedded heat sinks have been produced for high power density military platform CCAs. In Figure 4 the top diagram illustrates the basic arrangement of the CCA and prototype heat sink which is comprised of a Bottom Unit and Top Unit that sandwich the CCA to acquire heat from the CCA's devices and then conduct it to the Bottom Unit's rails. Heat is rejected by the Bottom Unit's rails which are in contact

with the ultimate heat rejection medium (e.g. pumped liquid,

forced air, *etc.*). Prior to prototyping, FEM predictions of a solid Al unit performance were compared to an OHP-embedded model. These initial models predicted that if the embedded channels assumed an axial-wise effective thermal conductivity of 1kW/m-K, then the maximum temperatures at the heat sink would drop by 2.5°C (compared to solid Al); and if the channels reached a 10kW/m-K effective thermal conductivity then the maximum temperatures would drop by 6.2°C. These levels of channel volume effective k<sub>thermal</sub> are within the bounds of previously achieved results of prior efforts of the authors (Figure 3) and other researchers [3, 5, 8, 17].

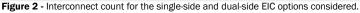

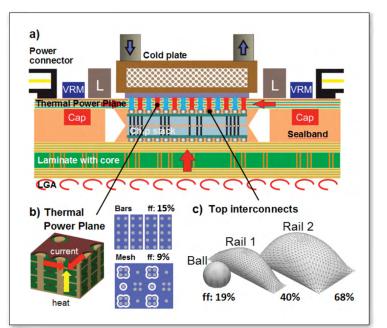

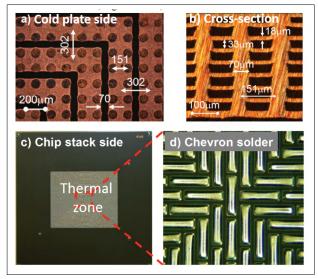

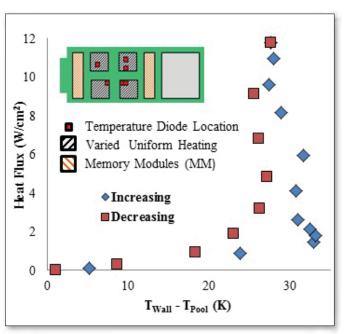

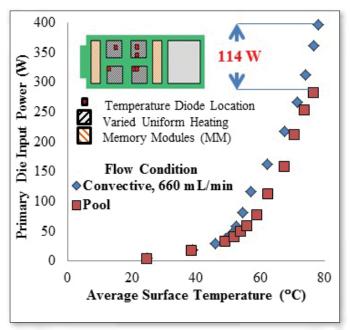

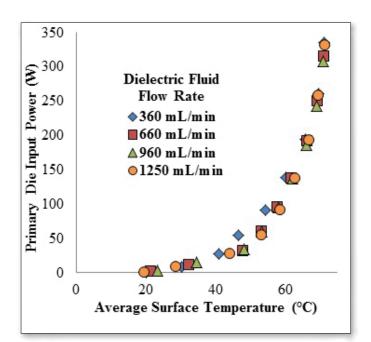

With these targets in place, prototype Bottom Units and Top Units were fabricated, both from solid Al 6061 ( $k_{thermal}$  = 167W/m-K) and from Al 6061 embedded with OHP channels as shown in Figure 4. The per unit price of the OHP-embedded units compared favorably to alternative high performance heat sink solutions.